9T3

-

Upload

stiva-darcy -

Category

Documents

-

view

14 -

download

3

description

Transcript of 9T3

Dpto. Tecnología Electrónica EC 10/March/09

Man

uel V

alen

cia

EC: Sistemas digitales a nivel RT

REALIZACIÓN DE SISTEMAS DIGITALES A NIVEL RTContenido:

Diseño de sistemas digitales: organización Datos&Control; macro y micro-opera-ciones; componentes; lenguaje RT; interconexión vía buses; realización de la unidad de datos. Un ejemplo: calculadora; desarrollo de la calculadora a nivel RT.

Descripción con cartas ASM: la construcción de cartas ASM; la carta de datos y la de control.

Diseño de la unidad de control: mediante un biestable por estado. Control microprogramado.

El uso de la calculadora.

Bibliografía básica

** C. Baena, I. Gómez, J.I. Escudero, M. Valencia: “Sistemas Digitales”. Servicio de publicaciones del Dpto. Tecnología Electrónica, 1997. Cap. 1 y 2

** C. Baena, M.J. Bellido, A. J. Molina, M.P. Parra, M. Valencia: “Problemas de Circuitos y Sistemas Digi-tales”. Ed. McGraw-Hill Interamericana, 1997. Caps 11 y 12.

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 2

NIVEL RT: DATOS Y CONTROL

CIRCUITOS VERSUS SISTEMAS

Máquina de estados finitos Instrucciones: OperacionesFuncionalidad

0, 1

Líneas (cables)

De conmutación

Combinacional yalmacenamiento (memoria)

Información

Conexión

Nivel/Lenguaje

Organización

Palabras de datos

Buses

RT (Register Transfer)

Procesado de datos y control

CIRCUITOS SISTEMAS

Puertas y biestablesComponentes MUX, ALU, ..., registros, ...

CircuitoCombinacional

z1zk

x1

xn

y1

yr

reloj

B1

Br

Unidad de Control

Unidad deProcesado

XIN

X Z

ZOUT

DIN DOUT

X : cualificadores o entradas de controlZ : comandos o salidas de controlD: datos

reloj

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 3

NIVEL RT: DATOS Y CONTROL

MACRO Y MICRO OPERACIONES

∗ Macro-operación: También llamada instrucción

• Es cada tarea que especifica previamente el usuario y que el sistema realizaautomáticamente

• En general el sistema tarda varios ciclos de reloj en su ejecución.

∗ Micro-operación o μop:

• Es cada tarea que el sistema realiza en un único ciclo de reloj

• En general consiste en una o varias transferencias entre registros (RT).

∗ Cuestiones de interés general:

• • • La forma de diseñar los Sistemas Digitales• • • Las formas de describir los Sistemas Digitales

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 4

NIVEL RT: DATOS Y CONTROL

METODOLOGÍA DE DISEÑO EN EL NIVEL RT (Top Down)

0/ Punto de partida: Descripción funcional a través del ISP

1/ Diseñar la Unidad/Ruta de DatosProceso en varios pasos: Se establece una arquitectura básica, se desarrollan las operaciones/instrucciones a nivel de micropoeraciones y se modifica la arquitectura básica de la unidad/ruta de datos

2/ Describir formalmente el comportamiento de datos y de control mediante un algoritmo (algoritmo del flujo de datos y de control)

3/ Diseñar la Unidad de Control

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 5

NIVEL RT: DATOS Y CONTROL

FORMAS DE DESCRIPCIÓN

UTILIDAD: En el proceso de diseño Como documentación

QUÉ DESCRIBIREstructura de la Unidad de Datos

Componentes secuenciales (registros), llamados también de memoriaComponentes combinacionales, llamados también unidades funcionales orecursos de cálculoComponentes de conexión (buses)

Microprograma de controlEstructura del controlador

FORMAS DE DESCRIPCIÓN:Gráficas

Orientadas al nivel estructural: dibujos/diagramas de circuitosOrientadas al nivel funcional: cartas ASM (Algorithmic State Machine)

HDL: Hardware Description Language

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 6

NIVEL RT: DATOS Y CONTROL

EJEMPLO DE SISTEMA DIGITAL

• Especificación inicial:

CALCULADORA DE SUMAS Y RESTAS: Cualquier posibilidad de suma o resta entre dos datos, A y B, y de almacenar el resultado en el registro que ocupaba uno de ellos

• Conjunto de instrucciones (ISP: Instruction Set Processor). Hay 8, que son:

• A ← A + B • B ← A + B • A ← A - B • B ← A - B• A ← -A + B • B ← -A + B • A ← -A - B • B ← -A - B

CONTROL A

B

U. PROCESADO

Z

IR[3]

XS

Usuario Sistema

FIN• Organización del sistema

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 7

NIVEL RT: DATOS Y CONTROL

• Modo de operación de calculadora

EL USUARIO:

Especifica en IR (Instruction Register) una de las ocho instrucciones.

Suministra la señal de comienzo XS.

EL SISTEMA:

Ejecuta la instrucción especificada.

Genera señal "FIN" y espera nueva XS.

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 8

NIVEL RT: DATOS Y CONTROL

NOTACIÓN RT. TIPOS DE OPERACIÓN

Operación Notación RT

Carga en paralelo Α ← DINDesplazamiento a dcha. An-1 ← Dr , Ai ← Ai+1 ∀i≠n-1 ; A ← ShR(A,Dr)Desplazamiento a izda. A0 ← Dl , Ai ← Ai-1 ∀i≠0 ; A ← ShL(A,Dl)Incremento (Decremento) A ← A+1 (A ← A-1)Puesta a 0 (ó a 1) A ← 0 (A ← 1...1)Inhibición (NOP) A ← A

De escritura

Operación Señal de control

Carga en paralelo W (T, L)Desplazamiento a dcha. / izda. SR / SLIncrementa / Decrementa I / DPuesta a 0 / 1 CL (Z) / SInhibición Ninguna activaLectura R

De controlIncondicional: Condicional

Dout = A R = 1 : Dout = AR = 0 : Dout = HI

Las operaciones de lectura pueden afectar a:

Todo el dato: Dout = AParte del dato: Outa = A3Una función del dato: Cero ={ 0 si A≠0

1 si A=0

De lectura

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 9

NIVEL RT: DATOS Y CONTROL

IMPLICACIÓN DE DATOS EN TRANSFERENCIA ENTRE REGISTROS

COMPONENTES DE MEMORIA: UD: Registros A, B C

Funciones: Escritura en A y Lectura de B yC

COMPONENTES COMBINACIONALES: Para implementar funciones:

En UD: el procesado de datos G(B, C, ...)En UC: la condición de control, f(x)

COMPONENTES DE CONEXIÓN: Caminos físicos y lógicos para el flujo de datos desde cada registro fuente al de destino:

• Líneas de conexión (buses)• Circuitos combinacionales

ADEMÁS, LA UC:Establece la secuencia de μOpsGenera las señales de control en UD

Operación RTf(x): A ← G(B, C, ...)

Condición de ejecución

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 10

NIVEL RT: DATOS Y CONTROL

Descripción estructural del Sistema digital

• Evalúa f(x)

• Genera señales de control

• Establece secuencia de RT

CircuitoCombinacional

que realiza

G(B, C, ...)

Δ

Δ

Δ

•

∇

CK

RB

WA

x

CONTROL DATOS

B

C

A

R

W

• • •

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 11

NIVEL RT: DATOS Y CONTROL

Operación temporal 1

• Evalúa f(x)

• Genera señales de control

• Establece secuencia de RT

CircuitoCombinacional

que realiza G(B, C, ...)

Δ

Δ

Δ

•

∇

CK

RB

WA

x

CONTROL DATOS

B

C

A

R

W

• • •

Ciclo K

Inicialmente los datos son: A0, B0 y C0

Suponemos f(x) = 1

Ck:

RB:

Sal B: Sal G:

A:

f(x): A ← G(B, C, ...)

G(B0, C0, ...)

HI HIB0G(B0, C0, ...)???

A0???

C0

WA:

ciclo K ciclo K+1ciclo K-1

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 12

NIVEL RT: DATOS Y CONTROL

Operación temporal 2

• Evalúa f(x)

• Genera señales de control

• Establece secuencia de RT

CircuitoCombinacional

que realiza G(B, C, ...)

Δ

Δ

Δ

•

∇

CK

RB

WA

x

CONTROL DATOS

B

C

A

R

W

• • •

Ciclo K

Inicialmente los datos son: A0, B0 y C0

Suponemos f(x) cambia

Ck:

RB:

Sal B: Sal G:

A:

f(x): A ← G(B, C, ...)

G(B0, C0, ...)

HI HI???A0

???

C0

WA:

f(x):

B0G(B0, C0, ...)

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 13

NIVEL RT: DATOS Y CONTROL

METODOLOGÍA DE DISEÑO EN EL NIVEL RT (Top Down)

Tras elegir el ISP del Sistema Digital:

1/ Diseñar la Unidad/Ruta de Datos (Data Path)Proceso en varios pasos:

Tratemos en primer lugar las interconexiones.

Bloque de

Registros

Interconexión

UnidadesFuncionales

Entradas Salidas

∗ Se establece una arquitec-tura básica,

∗ se desarrollan las opera-ciones/instrucciones a nivel de micropoera-ciones, y

∗ se modifica la arquitec-tura básica de la unidad/ruta de datos

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 14

NIVEL RT: DATOS Y CONTROL

INTERCONEXIÓN VÍA BUSES

B0B1

Bn-1

n

n

B[n] = B0:n-1{BUSB[n] = B0:n-1

• Bus: Conjunto de “n líneas” conductoras con un protocolo para su manejo

• Tipos de Buses

Estándar (0, 1)Unidireccional

Fuente Destino

Fu / De De / Fu

Bidireccional

Dedicados

Compartidos 3-state (0, 1, HI)

Salidaestándar

Buffer3-state

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 15

NIVEL RT: DATOS Y CONTROL

LECTURA DE BUS (con Escritura en Registro)A ← Bus = Dato

Único bus: Uno entre varios buses (p. ej. 4):Conexión directa Conexión multiplexada

WA = 1

A

DatoBus

Ej.: Dato = 1011Bus

WA = 1

A012

3

Bus 0Bus 1Bus 2

1

11

0

Bus 3

S1S0

00

1 1 2 3

WA = 1

A

Dato

10

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 16

NIVEL RT: DATOS Y CONTROL

ESCRITURA DE BUS (con Lectura en Registro) Bus = [A]

Sólo hay un registro fuente: la salida del registro puedeser estándar o 3-state

Hay varios registros fuente: deben ser 3-state

Bus único

A

Varios Buses

A

A3 A2 A1R1R2R3

Como máximo, una señal Rj activaP. ej. R1R2R3 = 0 1 0 para

Bus = [A2]

Recordad: las salidas bidireccionales(in/out) conllevan el carácter 3-state

0 01

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 17

NIVEL RT: DATOS Y CONTROL

EJEMPLO:

• Se dispone de 4 registros [n], A3, A2, A1, A0, con carga en paralelo (W3, W2, W1, W0)• Hay que realizar la conexión para la trasnferencia AF → AD, con F, D ∈ {0, 1, 2, 3}• La selección de Fuente está dada por F1F0 y la de Destino, por D1D0.

A3W

A2W

A1W

A0W

D1

D0

DEC2 : 4 3

2100

1

Ejemplo, AD = A1 (D=1)D1D0 = 0 1

01

000

1

Solución del Destino:

[AF]

Hay que garantizar [AF] en las entradas paralelo de AD = A1

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 18

NIVEL RT: DATOS Y CONTROL

CASO 1: Registros con entrada y salida separadas

1/ Con salida estándar Solución Multiplexada

A3W

n

A2W

n

A1W

n

A0W

n

D1

D0

DEC2 : 4 3

2100

101

0 0 01

F1F0 n x MUX 4 : 1

10

3210

AF = A3; F1F0 = 1 1

11

[A3]

Ejemplo, A3 → A1AD = A1

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 19

NIVEL RT: DATOS Y CONTROL

CASO 2: Registros con entrada y salida separadas

2/ Con salida 3-state Solución Bus (HI)

A3W

n

A2W

n

A1W

n

A0W

n

D1

D0

DEC2 : 4 3

2100

101

0 0 01

Ejemplo, A3 → A1

F1

F0

DEC2 : 4

3210

1

0

R R R R∇ ∇ ∇ ∇

11 1

000

[A3]

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 20

NIVEL RT: DATOS Y CONTROL

CASO 3: Registros con terminales de entrada/salida

Terminal bidireccional Solución Bus (HI)

A3W

A2W

A1W

A0W

D1

D0

DEC2 : 4 3

2100

101

0 0 01

Ejemplo, A3 → A1

F1

F0

DEC2 : 4

3210

1

0

R R R R∇ ∇ ∇ ∇

11

100 0

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 21

NIVEL RT: DATOS Y CONTROL

DISEÑO DE Data Path

• El Data Path tiene que poder ejecutar todas las μops • La organización del Data Path puede ser de propósito:

∗ Específico: Para una tarea concreta (p. ej. sumador serie de pág. siguiente)∗ General: Para muchas tareas (p. ej. el computador simple que diseñaremos)

• Estructura: nos centramos en Data Path síncronos disparados por flanco.

Bloque de

Reg RegReg Reg

Interconexión

UnidadFuncional

UnidadFuncional

Entradas Salidas COMPONENTES

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 22

NIVEL RT: DATOS Y CONTROL

REGISTROS VISIBLES POR EL USUARIO

• Registros visibles por el usuario: Aquéllos que aparecen en la descripción de las macrooperaciones (instrucciones)

• Los registros visibles son los únicos que el usuario necesita conocer.

• Registros visibles de la calculadora (pág. 6): A y B.

• Cuando se ejecuta una macrooperación no debe modificarse el contenido de ningún registro visible, a no ser que dicho registro aparezca como destino en una transferencia de la descripción de la macrooperación.

• Puede modificarse el contenido de cualquier registro no visible.

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 23

NIVEL RT: DATOS Y CONTROL

DATA PATH ESPECÍFICO: EJ. SUMADOR SERIE

xrWASRA 0DA[n]

Pin

ai biCiCi+1 FA

si

xrWBSRB 0DB[n]

Pin

xrSRS SUM[n]

inq

CNT mod. nCLUP

Cy

Din [n]

CD

WD

Control Unit

Data Path

Start End

Cy WA WB CL SRA SRB UP CD W SRS

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 24

NIVEL RT: DATOS Y CONTROL

ORGANIZACIONES GENÉRICAS BASADAS EN ALU:1. BUS SIMPLE

Ck R1 Ck R2 Ck Rk

. . .

Ck ACC

ALU

RTCk

Sumar R1 con R2 en Rk requiere varias μops:1 RT ← R12 ACC ← RT + R23 Rk ← ACC

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 25

NIVEL RT: DATOS Y CONTROL

2. DOBLE BUS

RT

ALU

B1

B2

Ck R1 Ck R2 Ck Rk

Ck

. . .

Sumar R1 con R2 en Rk requiere varias μops, pero menos:1 RT ← R12 Rk ← RT + R2

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 26

NIVEL RT: DATOS Y CONTROL

3. TRIPLE BUS

Sumar R1 con R2 en Rk requiere sólo 1 μop:Rk ← R1 + R2

ALU

Ck R1 Ck R2 Ck Rk

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 27

NIVEL RT: DATOS Y CONTROL

METODOLOGÍA DE DISEÑO EN EL NIVEL RT (Top Down)

1/ Diseñar la Unidad/Ruta de Datos (Data Path)∗ Elección de una arquitectura básica

∗ Desarrollo de cada macro-operación en una secuencia de micro-operaciones (μOp):• Instrucción o macro-operación: Ejecución en varios ciclos de Clk• Micro-operación: Una o más primitivas RT que se ejecutan en solo ciclo de Clk

∗ Cambios en la arquitectura básica de la unidad de datos para que ejecute todas las micro-operaciones.

Nivel ISP Nivel RTμOp RT1

Instrucción K μOp RT2

μOp RTN···

Cada macro-operación Secuencia de micro-operaciones

Este paso afecta y dependede la Unidad de Datos

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 28

NIVEL RT: DATOS Y CONTROL

DISEÑO DE LA CALCULADORA

a b

a±b

ACΔ

T

ΔWT

A

ZACWACRAC

WARA

Δ BWBRB

sr

[AC]

DBTodo de n bits

UNIDAD DE PROCESADO

WT sWB RAC WACrWA RBRA ZAC

(del controlador)

Descripción de componentes

Ejemplo: Registro A (B)

Δ AWARAV

Estructural

Funcional

RA WA A ← V =

0 0 A ← A V = HI

0 1 A ← V V = DIN

1 0 A ← A V = [A]

1 1 Prohibida

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 29

NIVEL RT: DATOS Y CONTROL

INSTRUCCIONES → SECUENCIA DE MOPS

Α←Α+Β Β←Α+Β Α←Α−Β Β←Α−Β

ΑC←0, Τ←Α

ΑC←AC+T ΑC←AC-T

Α←ΑC Β←ΑC Α←ΑC Β←ΑC

μOP

T0

T1

T2

T3

Τ←B , ΑC←AC+T

Α←(−Α)+Β Β←(−Α)+Β Α←(−Α)−Β Β←(−Α)−Β

ΑC←0, Τ←Α

ΑC←AC+T ΑC←AC-T

Α←ΑC Β←ΑC Α←ΑC Β←ΑC

μOP

T0

T1

T2

T3

Τ←B , ΑC←AC-T

Dpto. Tecnología Electrónica EC Nivel RT Datos y Control - 30

NIVEL RT: DATOS Y CONTROL

TAREAS PENDIENTES

Realizar los siguientes pasos de la Metodología de diseño, que son:

2/ Describir formalmente el comportamiento de datos y de control mediante un algoritmo (algoritmo del flujo de datos y de control)

3/ Diseñar la Unidad de Control

Dpto. Tecnología Electrónica EC 19/February/09

Man

uel V

alen

cia

EC: Sistemas digitales a nivel RT

REALIZACIÓN DE SISTEMAS DIGITALES A NIVEL RTContenido:

Diseño de sistemas digitales: organización Datos&Control; macro y micro-operaciones; componentes; lenguaje RT; interconexión vía buses; realización de la unidad de datos. Un ejemplo: calculadora; desarrollo de la calcu-ladora a nivel RT.

Descripción con cartas ASM: la construcción de cartas ASM; la carta de datos y la de control.

Diseño de la unidad de control: mediante un biestable por estado.

El uso de la calculadora.

Bibliografía básica

** C. Baena, I. Gómez, J.I. Escudero, M. Valencia: “Sistemas Digitales”. Servicio de publicaciones del Dpto. Tecnología Electrónica, 1997. Cap. 1 y 2

** C. Baena, M.J. Bellido, A. J. Molina, M.P. Parra, M. Valencia: “Problemas de Circuitos y Sistemas Digi-tales”. Ed. McGraw-Hill Interamericana, 1997. Caps 11 y 12.

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 2

CARTAS ASM

CARTA ASM: DEFINICIONES

Caja de EstadoCaja de Decisión

Caja de Acción Condicional

Símbolode estado

Camino deentrada

Caminode salida

Accionesbbb Código binario

S CondiciónSí No

Caminode salida

Caminode salida

Camino de entrada

Acciones

Camino de entrada

Camino de salidaUniones de caminos:

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 3

CARTAS ASM

Bloque ASM

. . . . . . . . .

. . .

Un camino de entrada

Una y sólo una

caja de estados

Número variable

de acción condicional

de cajas de decisión o

Número variable de caminos de salida

Carta ASM

Grafo orientadoy cerrado

que interconectabloques ASM

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 4

CARTAS ASMContador ascendente mód. 8

Binario(G=0)/Gray(G=1)

G

G

G

G

G

G

z0

z1

z1 z0

z2

z2 z0

z1z2

z2 z1 z0

1

0

1

0

0

1

0

1

1

0

0

1

Moore

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 5

CARTAS ASMContador ascendente mód. 8

Binario(G=0)/Gray(G=1)

G

G

G

G

G

G

z0

z1

z1 z0

z2

z2 z0

z1z2

z2 z1 z0

1

0

1

0

0

1

0

1

1

0

0

1

Moore

G

z1

10

z0

z0

z1

z2

Mealy

G0 1

z0

G10

z1

z2 z0

G10

z1

z2

G10

z0z1

z2

G

z1 z0

10

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 6

CARTAS ASM

Máquina expendedora

s1A

CK

s0

R

C

s1 s0 Moneda

0 0 Ninguna0 1 11 0 21 1 5

ESPECIFICACIÓN

• Producto de valor 4 €.

• Admite billete de 5 y monedas de 2 y 1 €.

• Con 5 € da cambio (para ello, activa C=1).

• Se accede al producto (para ello, activa A=1).

• R causa directamente el retorno de las mone-das (el controlador no tiene que activar C).

Rs1s0

0 1

C, A5 11 00

01102 1

R R 1

s1s0s1s0

1

0 000 000110

01 10

3

R 10

s1s0= 00≠ 00

4A

Carta ASM

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 7

CARTAS ASM

Errores comunes en la construcción de cartas ASM

Próximo estado

Cartas con error

A

B C

x y

A

B C D

0 1 0 1

sin determinar

x

A

B

01

Cerrar lazos sincajas de estado

x

A

B

01

x

A

10

y 01

x 10

B

x⋅y

A

0 1

x+y

B

01

No garantizar la posibilidad lógicade todos los caminos

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 8

CARTAS ASM

Consideraciones temporales

A

M N

XRAWMWN

CK

RA

WM WN

•

•

DATOS∇C

ON

TR

OL

SISTEMA OPERACIÓN ASM: Datos y Control

X

SK

0 1

N←A

M←Α

SK+1. . . .

X

SK

0 1

WN

RA,WM

SK+1. . . .

SKSK-1 SK+1

CkSX

RA

WM

WN

[M]

[N]

M0 A0M0

N0 N0 A0

[A] = A0

FORMAS DE ONDA

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 9

CARTAS ASM

Inicio y Fin de operación

XS

Carta ASM del ejemplo

FINSF

0

1

S0 NOP

Puede ser unestado útil o unaacción condicional

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 10

CARTAS ASM

Carta ASM de la Calculadora: de Datos

IR210

Xs0

1

IR110

IR010

ΑC←0, Τ←Α

Τ←B

ΑC←AC+T

S0

S1

S2

S3

S4

SF

q2q1q0=000

q2q1q0=001

q2q1q0=010

q2q1q0=011

q2q1q0=100

q2q1q0=101

IR2:0 μOP0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1

A ← A+BΒ ← A+BA ← A -BΒ ← A -BA ← -A+BΒ ← -A+BA ← -A -BΒ ← -A -B

Α← Α+Β Β←Α+Β Α←Α−Β Β←Α−Β

ΑC←0, Τ←Α

ΑC←AC+T ΑC←AC-T

Α←ΑC Β←ΑC Α←ΑC Β←ΑC

μOP

1

2

3

4

Τ←B , ΑC←AC+T

Si es AoB ← - A+B, en μOP 2 se hará ΑC←AC-T

ΑC←AC-T

ΑC←AC+T ΑC←AC-T

Β←ΑCΑ←ΑC

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 11

CARTAS ASM

Carta ASM de la Calculadora: de Control

IR210

Xs0

1

IR110

IR010

ZAC, WT, RA

WAC, WT, RB

s r

s r

WA WB

S0

S1

S2

S3

S4

SF

WAC

RAC

q2q1q0=000

q2q1q0=001

q2q1q0=010

q2q1q0=011

q2q1q0=100

q2q1q0=101

IR210

Xs0

1

IR110

IR010

ΑC←0, Τ←Α

Τ←B

ΑC←AC+T

S0

S1

S2

S3

S4

SF

q2q1q0=000

q2q1q0=001

q2q1q0=010

q2q1q0=011

q2q1q0=100

q2q1q0=101

ΑC←AC-T

ΑC←AC+T ΑC←AC-T

Β←ΑCΑ←ΑC

FIN

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 12

CARTAS ASM

HDL básico (FSMD:Finite State Machine with Data path)FORMATO GENERAL:

CASOS PARTICULARES:

N fi(x) Ti/zi [N+1] Puede eliminarse la próxima μOP si es N+1

N t NOP Nk Sin condición es “t” (true); sin acción es NOP

N f(x) T0/z0 N0 Puede ponerse N IF f(x) THEN T0/z0 goto N0f(x) T1/z1 N1 ELSE T1/z1 goto N1

N t NOP Nk Puede ponerse N goto Nk

N f0(x) T0/z0 N0 f1(x) T1/z1 N1 ... ... ...fk(x) Tk/zk Nk

μop actual próxima μop

condicionesAcciones

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 13

CARTAS ASM

RELACIÓN ENTRE CARTAS ASM Y HDL

4M

N P

5 6

x

4 x M/P 6

1 0

x M/N

Tipo Moore

Tipo Mealy

Dpto. Tecnología Electrónica EC Nivel RT Cartas ASM - 14

CARTAS ASM

HDL de la Calculadora

000 Xs - 000

Xs - 001

001 t ZAC/WT/RA 010

010 IR2 WT/RB/WAC/s 011

IR2 WT/RB/WAC/r 011

011 IR1 WAC/s 100

IR1 WAC/r 100

100 IR0 RAC/WA 101

IR0 RAC/WB 101

101 t FIN 000

IR210

Xs0

1

IR110

IR010

ZAC, WT, RA

WAC, WT, RB

s r

s r

WA WB

S0

S1

S2

S3

S4

SF

WAC

RAC

q2q1q0=000

q2q1q0=001

q2q1q0=010

q2q1q0=011

q2q1q0=100

q2q1q0=101 FIN

Dpto. Tecnología Electrónica EC Sistemas Digitales a nivel RT 19/2/09

Man

uel V

alen

cia

REALIZACIÓN DE SISTEMAS DIGITALES A NIVEL RTContenido:

Diseño de una calculadora: organización Datos&Control; macro y micro-operaciones; componentes; len-guaje RT; interconexión vía buses; realización de la unidad de datos; desarrollo de la calculadora a nivel RT.

Descripción con cartas ASM: la construcción de cartas ASM; la carta de datos y la de control.

Diseño de la unidad de control: mediante un biestable por estado. El uso de la calculadora.

Bibliografía básica

** C. Baena, I. Gómez, J.I. Escudero, M. Valencia: “Sistemas Digitales”. Servicio de publicaciones del Dpto. Tecnología Electrónica, 1997. Cap. 1 y 2

** C. Baena, M.J. Bellido, A. J. Molina, M.P. Parra, M. Valencia: “Problemas de Circuitos y Sistemas Digita-les”. Ed. McGraw-Hill Interamericana, 1997. Caps 11 y 12.

Dpto. Tecnología Electrónica EC Unidad de Control - 2

UNIDAD DE CONTROL

Generalidades

∗ Objetivo: Diseñar la Unidad de control

∗∗ El punto de partida es el microprograma, bien como carta ASM, bien en HDL

∗∗ Nuestro interés: automatizar proceso de diseño y lograr buen circuito.

∗ Técnicas:

∗∗ CSS estándar, con biestables y puertas (Random logic): Proceso clásico para CSS

∗∗ Con 1 biestable por estado

∗∗ Control Microprogramado en ROM o PLA (firmware)

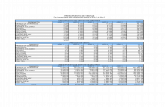

∗ Comparación:Técnica Proceso diseño Prestaciones Repetibilidad

CSS estándar Complejo Muy buenas Compleja1 biestable por estado Muy sencillo Buenas, pero mejorables Algo complejaFirmware Sencillo Regulares Fácil

Dpto. Tecnología Electrónica EC Unidad de Control - 3

UNIDAD DE CONTROL

Calculadora: Carta ASM y HDL HDL DE LA CALCULADORA

000 Xs - 000

Xs - 001

001 t ZAC/WT/RA 010

010 IR2 WT/RB/WAC/s 011

IR2 WT/RB/WAC/r 011

011 IR1 WAC/s 100

IR1 WAC/r 100

100 IR0 RAC/WA 101

IR0 RAC/WB 101

101 t FIN 000

IR210

Xs0

1

IR110

IR010

ZAC, WT, RA

WAC, WT, RB

s r

s r

WA WB

S0

S1

S2

S3

S4

SF

WAC

RAC

q2q1q0=000

q2q1q0=001

q2q1q0=010

q2q1q0=011

q2q1q0=100

q2q1q0=101

CARTA ASM DE LA CALCULADORA

Dpto. Tecnología Electrónica EC Unidad de Control - 4

UNIDAD DE CONTROL

1 biestable por estado

∗ Los estados tienen codificación one-hot, salvo el de espera que tiene código 00...0:μop q1q2q3q4...1 1 0 0 0...2 0 1 0 0...3 0 0 1 0...4 0 0 0 1...

∗ Una visión intuitiva: con xS se introduce un 1 en el biestable de μop1 y ese 1 va circu-lando conforme se pasa de una μop a otra∗ Se puede automatizar el paso desde carta ASM al circuito

m

v

Sk

D

q

Clk

vm

m

KB

v0x

v1

0 1

x

mv0

v1

m0 m1

v

>1v

m0

m1

m1

Bmp

m

v

SkB

>1qk

mp

ASM

Circuito

Dpto. Tecnología Electrónica EC Unidad de Control - 5

UNIDAD DE CONTROL

IR210

Xs0

1

IR110

IR010

ZAC, WT, RA

WAC, WT, RB

s r

s r

WA WB

S0

S1

S2

S3

S4

SF

WAC

RAC

q5-q1=0...0

q1=1

q2=1

q3=1

q4=1

q5=1

CARTA ASM DE LA CALCULADORA CONTROL CON 1 BIESTABLE POR ESTADO

D q1

D q2

D q3

D q4

D qF(5)

Xs

RA ZAC

IR2

0

1

r s IR1

0

1

r s

WT WT

>1 WT

FIN

IR0

0

1

WBWA

RB

>1 WAC

WACWAC

>1r

>1s

RAC

FIN

Clk

Dpto. Tecnología Electrónica EC Unidad de Control - 6

UNIDAD DE CONTROL

Control microprogramado (firmware)

N f0(x) T0/z0 N0 f1(x) T1/z1 N1 ... ... ...fk(x) Tk/zk Nk

Instrucción genérica en HDL

ROM/PLA

Ent

rada

s

Salidas

Próxima Salidasde controlμop

x

N = [Reg]: actual μop

N+

Reg

Reg: Registro de carga en paralelo

Comandos

Nk zk

Unidad de control

Cualificadores

El valor de N y fk(x)dan la dirección deentrada en cuya palabra

están escritas Nk y zk

Dpto. Tecnología Electrónica EC Unidad de Control - 7

UNIDAD DE CONTROL

IR210

Xs0

1

IR110

IR010

ZAC, WT, RA

WAC, WT, RB

s r

s r

WA WB

S0

S1

S2

S3

S4

SF

WAC

RAC

q2q1q0=000

q2q1q0=001

q2q1q0=010

q2q1q0=011

q2q1q0=100

q2q1q0=101

CARTA ASM DE LA CALCULADORA CONTROL CON PLA

q2q1q0 Q2Q1Q0 Término P Salidas afectadas

000 Xs NOP 000

Xs NOP 001 Xsq2q1q0 Q0

001 t ZAC/WT/RA 010 q2q1q0 Q1, ZAC/WT/RA

010 IR2 WT/RB/WAC/s 011 IR2q2q1q0 Q1Q0, WT/RB/WAC/s

IR2 WT/RB/WAC/r 011 IR2q2q1q0 Q1Q0, WT/RB/WAC/r

011 IR1 WAC/s 100 IR1q2q1q0 Q2, WAC/s

IR1 WAC/r 100 IR1q2q1q0 Q2, WAC/r

100 IR0 RAC/WA 101 IR0q2q1q0 Q2Q0, RAC/WA

IR0 RAC/WB 101 IR0q2q1q0 Q2Q0, RAC/WB

101 t FIN 000 q2q1q0 FIN

Dpto. Tecnología Electrónica EC Unidad de Control - 8

UNIDAD DE CONTROL

PERSONALIZACIÓN DEL PLA

Términos P Salidas afectadas (D=Q)

Xsq2q1q0 Q0

q2q1q0 Q1, ZAC/WT/RA

IR2q2q1q0 Q1Q0, WT/RB/WAC/s

IR2q2q1q0 Q1Q0, WT/RB/WAC/r

IR1q2q1q0 Q2, WAC/s

IR1q2q1q0 Q2, WAC/r

IR0q2q1q0 Q2Q0, RAC/WA

IR0q2q1q0 Q2Q0, RAC/WB

q2q1q0 FIN

Xs

D q0

D q1

D q2IR2

IR1

IR0

q2

q1 q0

ZACWTRARBWACsrRACWAFIN WB

Plano AND Plano OR

Xsq2q1q0

q2q1q0

IR2q2q1q0

IR2q2q1q0

IR1q2q1q0

IR1q2q1q0

IR0q2q1q0

IR0q2q1q0

q2q1q0

Clk

Dpto. Tecnología Electrónica EC Unidad de Control - 9

UNIDAD DE CONTROL

DISEÑO CON ROM

A2A1A0 A3 Salidas D2D1D0

q2q1q0 E Salidas Q2Q1Q0

000 Xs - 000

Xs - 001

001 t ZAC/WT/RA 010

010 IR2 WT/RB/WAC/s 011

IR2 WT/RB/WAC/r 011

011 IR1 WAC/s 100

IR1 WAC/r 100

100 IR0 RAC/WA 101

IR0 RAC/WB 101

101 t FIN 000

D q0

D q1

D q2

Clk

6

012345

7

Xs

IR2IR1IR0

EROM 24x14

3210

Salidas [14]

{A3A2A1A0} {D2D1}{D0 ZAC WT RA} {RB WAC s r} {RAC WA WB FIN}

D2D1D0

ZACWTRARBWACsrRACWAWBFIN

Ejemplos de contenidos de la ROM:

0000 00 0000 0000 00001000 00 1000 0000 00000001 01 0111 0000 00001001 01 0111 0000 0000

Dpto. Tecnología Electrónica EC Unidad de Control - 10

UNIDAD DE CONTROL

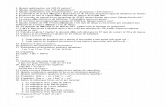

Contenidos de la ROM

$A={A3A2A1A0}

$H3={D2D1}$H2={D0 ZAC WT RA}$H1={RB WAC s r}$H0={RAC WA WB FIN}

$A $H3H2H1H0

0 0000

1 1700

2 1AE0

3 2060

4 280C

5 0001

6 (0000)

7 (0000)

8 0800

9 1700

A 1AD0

B 2050

C 280A

D 0001

E (0000)

F (0000)

(Ejemplos Anteriores)

(0000): No importa en este caso

Dpto. Tecnología Electrónica EC 19 / February / 09

Man

uel V

alen

cia

REALIZACIÓN DE SISTEMAS DIGITALES A NIVEL RTContenido:

Diseño de una calculadora: organización Datos&Control; macro y micro-operaciones; componentes; len-guaje RT; interconexión vía buses; realización de la unidad de datos; desarrollo de la calculadora a nivel RT.

Descripción con cartas ASM: la construcción de cartas ASM; la carta de datos y la de control.

Diseño de la unidad de control: mediante un biestable por estado.

El uso de la calculadora.

Bibliografía básica

** C. Baena, I. Gómez, J.I. Escudero, M. Valencia: “Sistemas Digitales”. Servicio de publicaciones del Dpto. Tecnología Electrónica, 1997. Cap. 1 y 2

** C. Baena, M.J. Bellido, A. J. Molina, M.P. Parra, M. Valencia: “Problemas de Circuitos y Sistemas Digi-tales”. Ed. McGraw-Hill Interamericana, 1997. Caps 11 y 12.

EC: Sistemas digitales a nivel RT

Dpto. Tecnología Electrónica EC Nivel RT Uso de la calculadora- 2

USO DE LA CALCULADORA

Problema a resolver con la Calculadora:

• Calcular 3A-B y poner el resultado en A

• Programa a ejecutar:

A0 B0

A BValores en A/B

Instrucción 1 : B ← A-B

Instrucción 2 : B ← A+B

Instrucción 3 : A ← A+B

A0 A0-B0

A0 2A0-B0

3A0-B0 2A0-B0

Valores iniciales:

Dpto. Tecnología Electrónica EC Nivel RT Uso de la calculadora- 3

USO DE LA CALCULADORA

• Funcionamiento ‘operativo’ de este sistema: Modo Calculadora

Problemas de funcionamiento del Modo Calculadora:

No hay programa almacenado ( , , )

Hay que generar la orden XS ( )

Solución a estos problemas en el Modo Computador de operación (Tema próximo)

“Alguien” pone IR=011 ( Β ← A - B )

“Alguien” da : XS

“Alguien” pone IR=001 ( Β ← A + B )

“Alguien” da: XS

“Alguien” pone IR=000 ( Α ← A + B )

“Alguien” da: XS

y espera a que se active FIN

y espera a que se active FIN

y espera a que se active FIN