Arquitectura interna y externa del microcontrolador. primer microprocesador comercial fue el Intel...

Transcript of Arquitectura interna y externa del microcontrolador. primer microprocesador comercial fue el Intel...

2

Índice Objetivo Microprocesador Microcomputador (PC) Microcontrolador Procesador de señales digitales Sistema on a Chip programable (PSoC) Arquitectura de un microprocesador

– Von Neuman– Harvard– Conjunto de instrucciones

• CISC• RISC

Multiproceso

3

Objetivo

Repasar los componentes principales y elementos que integran a los microcontroladores y micro-procesadores así como de algunas de las variantes presentes en el mercado.

El alumno aprenderá las principales características de las diferentes arquitecturas de procesadores digitales y entenderá las ventajas y limitaciones de cada una de ellas.

Al finalizar el curso el alumno deberá ser capaz de identificar las características más importantes que cualquier proyecto requiera y deberá poder definir la plataforma idónea para los requerimientos del caso.

4

Microprocesador Microprocesador: Es un circuito integrado constituido por millones de

componentes electrónicos (como transistores, resistencias, etc). Su principal componente es la unidad central de procesamiento (CPU), la cual es la encargada de ejecutar las instrucciones programadas.

El CPU está constituido esencialmente, por registros, una unidad de control, una unidad aritmético lógica (ALU) y en algunos casos una unidad de cálculo de coma flotante (también conocido como «coprocesador matemático»).

Puede estar compuesto por varios núcleos. Un núcleo físico se refiere a una porción interna del microprocesador cuasi-independiente que realiza todas las actividades típicas de un CPU. Un núcleo lógico es la simulación de un núcleo físico implementado por software a fin de ejecutar de manera más eficiente el procesamiento.

Existe una tendencia de integrar el mayor número de elementos dentro del solo procesador, con lo que se aumenta su eficiencia energética y la miniaturización de todo el sistema. Entre los elementos integrados están: las unidades de punto flotante, los controladores de la memoria (RAM o ROM), los controladores de buses y los procesadores dedicados al video.

5

Computadora personal (Microcomputador)

Un microcomputador es una computadora que tiene un micro-procesador como unidad central de procesamiento.

Generalmente, el microprocesador incluye algunos circuitos de almacenamiento temporal (o memoria caché) y los de interfaces de entrada/salida dentro del mismo encapsulado (o circuito integrado). El primer microprocesador comercial fue el Intel 4004, que salió al mercado en Noviembre de 1971.

El microcomputador cuenta con dispositivos de acceso o entrada, tales como teclados o ratones, así como de salida, tales como monitores o impresoras. Su velocidad de procesamiento alcanza decenas de millones de instrucciones por segundo y por lo general está destinada al uso personal (a diferencia de los servidores).

6

Microcontrolador Microcontrolador: circuito integrado programable, capaz de ejecutar las

órdenes grabadas en su memoria. Está compuesto de varios bloques funcionales, los cuales cumplen una tarea específica.

Un microcontrolador incluye las tres principales unidades funcionales de una computadora

– Unidad central de procesamiento,

– Memoria

– Periféricos de entrada/salida)

– más una serie de módulos e interfaces y periféricos específicos

• Dispositivos de comunicación

• Entradas/salidas analógicas o digitales

Algunos microcontroladores pueden utilizar palabras de hasta 4 bits

Funcionar con frecuencias de reloj tan bajas como 4 kHz,

Consumir muy poca corriente (mW o microvatios)

7

Microcontrolador

Algunos microcontroladores poseen conjuntos avanzados de instrucciones y altas velocidades de procesamiento similar a un procesador digital de señales (DSP).

Tener capacidad para pasar a modo de inactividad y quedar en espera de algún evento como la activación de una interrupción, para reactivarse. El consumo de energía durante el estado de hibernación puede llegar a ser de tan sólo unos cuantos nanovatios.

Estos dispositivos pueden ser programados tanto en lenguaje ensamblador como en algún otro lenguaje para microcontroladores (inclusive de alto nivel). Sin embargo, para que el programa pueda ser internamente decodificado por el microcontrolador, éste deberá ser convertido al formato hexadecimal.

8

Procesador digital de señales (DSP) Un procesador digital de señales o DSP (digital signal processor) es un

procesador que posee un conjunto de instrucciones y un hardware optimizados para aplicaciones que requieran operaciones numéricas intensivas y a muy alta velocidad.

Son especialmente útiles para el procesamiento de señales analógicas en tiempo real, donde las muestras se reciben generalmente a través de convertidores analogo/digitales (ADC) y sus salidas están acopladas a algún tipo de convertidor digital/analógico (DAC) o algún otro tipo de salida digital modulada tal como PWM.

Como todo sistema basado en algún procesador programable, necesita una memoria donde almacenar tanto los datos e instrucciones; por lo general estas memorias están separadas para aumentar su velocidad.

Las principales aplicaciones para estos dispositivos son aquellas donde se aprovechan sus capacidades de procesamiento matemático y de cálculo en paralelo. Ambas características constituyen la principal diferencia entre un DSP y otros tipos de procesadores.

Programmable System-on-Chip (PSoC) La arquitectura PSoC consiste de bloques de elementos análogos o

digitales configurables, junto a un CPU programable. Este sistema permite el uso de módulos predefinidos (ya previamente validados) contenidos en las librerías del sistema de desarrollo.

La unión de varios bloques análogos o digitales no sólo permite ajustar sus capacidades de acuerdo a determinada aplicación, sino también expandirlas (e.g.: la conjunción de varios bloques digitales permite crear sistemas de 16-, 24- o 32-bits).

Lo módulos análogos están compuestos por diversos amplificadores operacionales, comparadores, etapas de switcheo, convertidores (ADC/DAC) y filtros digitales.

La interconexión de dichos módulos en completamente configurable por el usuario

El CPU está basado en arquitectura 8031 o ARM Cortex M3 e incluye módulos de memoria SRAM , EEPROM, y Flash junto con algunos recursos de sistema como:

– Osciladores principal y de bajo desempeño

– Etapa de reloj/contador programable

– Modos de Sleep y watchdog timers Variedad de fuentes de reloj incluyendo módulo de PLL Además los PSoC incluyen interfaces de comunicación dedicadas como:

I2C, USB 2.0, CAN 2.0, Serial y JTAG.

Programmable System-on-Chip (PSoC)Características del ambiente de desarrollo:

Interface gráfica (GUI) para la configuración de los bloques del PsoC, su Interconexión y ruteo a las terminales del encapsulado.

Capacidad de definición de módulos por parte del usuario (pre-configuración, pre-caracterización de los bloques y módulos). Documentación de interfaces y soporte para la implementación bloques.

Herramientas de depuración avanzadas con capacidad de visualización de registros, colocación de marcas (breackpoints) y visualización de transiciones dinámicas.

http://www.cypress.com/psoc1.

11

Sistemas PC / SoC embebidos Sectores industriales y militares comenzaron su uso en ciertas aplicaciones

donde la capacidad de computo de los microcontroladores estaba limitada.

El uso de los modernos sistemas PC basados en procesadores de propósito general (GPP) en aplicaciones embebidas generó numerosas ventajas:

Posibilidad de utilizar sistemas operativos potentes: comunicaciones por redes de datos, soporte gráfico, concurrencia con lanzamiento de hilos, etc.

Estos sistemas operativos pueden ser los mismos que para PC de escritorio (Linux, QNX, LynxOS, Windows CE, Windows NT Embedded) o bien ser versiones reducidas de los mismos, con características orientadas a los PC embebidos.

Dichos sistemas operativos permiten acceder a variedad de herramientas de desarrollo así como a diferentes utilerías y aplicaciones.

Reducen los costos del hardware y software debido que el mercado de consumo soporta su desarrollo.

Posibilidad de programación en otros lenguajes distintos a ensamblador o lenguaje C.

Per

iféric

osP

erifé

ricos

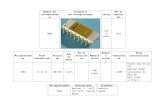

Un procesador consta principalmente de cinco: CPU, Memoria primaria (RAM ROM), dispositivos de entrada-salida, conjunto de buses (direcciones, datos y control) y la unidad de reloj.

La unidad central de procesamiento es la unidad que aporta la capacidad de cómputo al sistema.

Arquitectura de un microprocesador

Microprocesador Microprocesador

Memoria ROM

Memoria ROM

Memoria RAM

Memoria RAM

Interface de

entradas y salidas

Interface de

entradas y salidas

Bus de Direcciones

Bus de Control

Bus de Datos

Reloj

Reloj

Unidad Central de Procesamiento (CPU)

Unidad Central de Procesamiento (CPU)

ALUALUUnidad

de control

Unidad de

control

RegistrosRegistros

Diseño discreto. Se requiere:– Un microprocesador– 20+ líneas de buses (2 chips de 16 c/u)– 1 Interfaz serie (1 chip)– 1 Timer o cristal– Memoria SRAM (para variables)– Memoria Flash (para programa)– Memoria EEPROM (para constantes)

Arquitectura de un microprocesador

Oferta de Microcontroladores

Estructurada por “familias” y “subfamilias”.

Por ejemplo, cada familia tiene el mismo núcleo del procesador (su código será compatible): 8051,PIC,HC,ARM

O son familias orientadas a la aplicación

O por desempeño (de diferente tipo)

Arquitectura de un microprocesador

Dentro de cada “familia” hay mucha variedad de dispositivos

Pueden estar agrupados en “subfamilias”

Una forma de clasificación es en base a los periféricos que integran o memoria

Oferta de Microcontroladores

Arquitectura de un microprocesador

– Por stack– Por acumulador– Dos direcciones– Tres direcciones

Tipos de instrucciones

Arquitectura de un microprocesador

Modo de direccionamiento INMEDIATO

Arquitectura de un microprocesador

Registro: el operando es un registro que contiene el dato.

Inmediato: el operando es el dato. LOAD R1, #33

33R1

Modo de direccionamiento DIRECTO

Arquitectura de un microprocesador

Registro: el operando es un registro que contiene el dato.

Inmediato: el operando es el dato. LOAD R1, 2000

2124R1

2124

124

147

76...

Banco de Memoria:

2001

2002

2124

2000

Modo de direccionamiento INDIRECTO

Arquitectura de un microprocesador

Registro: el operando es un registro que contiene el dato.

Inmediato: el operando es el dato. LOAD R1, (2000)

147R1

2124

124

147

76...

Banco de Memoria:

2001

2002

2124

2000

Registros (memoria de corto plazo):– Pequeña (relativamente)– Almacenamiento temporal para uso del CPU

Memoria de datos– Relativamente Grande– Almacena datos mientras el MCU funciona

Memoria de programa– Relativamente Grande– De preferencia, mantiene el programa incluso con el

MCU apagado.

Memoria

Arquitectura de un microprocesador

S/DRAM: sin limite de escrituras

EEPROM: 100.000 ciclos de borrado

Flash: 10.000 ciclos de borrado

Memoria

Arquitectura de un microprocesador

Separada:– Cada tipo físico se direcciona por separado (por

ejemplo, usando diferentes registros índices)– Hay direcciones repetidas

Contínua:– Se accede siempre igual y la lógica interna accede a la

memoria que corresponde– No hay direcciones repetidas

Memoria

Arquitectura de un microprocesador

For (i=100;i>=0;i--)Inadvertidamente i es almacenada en EEPROMInadvertidamente i esta implementada como unsignedComo la EEPROM es lenta, cada iteración lleva, digamos, 10 ms¿Que pasa al conectar el MCU?:

– el programa se cuelga– Me doy cuenta, digamos, a los 10 segundos– Empiezo a “debuggear” el programa (pero no apago el MCU)

¿En cuanto tiempo me quedo sin microcontrolador?

Memoria: Ejercicio

Arquitectura de un microprocesador

Implementadas por pines de conexión directa al exterior:

– Los MCU tienen en general de 8 a 32 pines (o más).– Se agrupan en “ports” de a 8 pines.– En general, los pines se pueden configurar como

entrada o salida– La lógica puede ser positiva o negativa.– Los pines pueden tener otras funciones alternativas.

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

•pin 1 del port B

•Módulo de Interrupción 1 - entrada 5

•Pin Tx de puerto serie

•Conversor AD canal 5

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

Los pines se controlan mediante 3 registros:– Data Direction Register (DDR): hay uno por cada

puerto y cada bit determina la dirección de un pin.– Port Register (PORT): uno por cada puerto y cada bit

controla el estado del puerto (si es de salida)– Port Input Register (PIN): uno por cada puerto y cada

bit da el estado de su respectivo pin, esté este configurado como entrada o salida.

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

PTBDD = 0x80; // initialize PTB7 as output PTBD = 0; // initialize PTB to 0 PTBD_PTBD7 = ~PTBD_PTBD7; // invert the output

1000 0000

Ejemplo:bit 7 bit 0

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

PORT Register: de preferencia debe escribirse con operaciones de escritura de bit, si estan disponibles

Caso contrario usar : Read-Modify-Write con cuidado.

PDIR |= 0x42; // PDIR = PDIR | 0x42

PDIR = 0x42; // PDIR = 0x42

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

La entrada se muestrea con cada pulso (flanco ascendente normalmente) del clock, lo que ocasiona “metaestabilidad”:

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

Normalmente incorporan un Schmitt-trigger.

Para reducir la “metaestabilidad” se introducen “sincronizadores”

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

Cancelación de ruidos

Resistencias de pull-up/down en las entradas: puede (debe) programarse su conexión/desconexión (a veces mediante el registro PORT).

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

● Apenas el DDR configura un pin como salida, el MCU configura el nivel de salida del pin de acuerdo al contenido del registro PORT correspondiente.● Cuidado con los cortocircuitos● Orden de configuración de DDR y PORT

Entradas y salidas digitales (GPIO)

Arquitectura de un microprocesador

Unidad de Control:

• Registro de Instrucciones

• Contador de programa

• Decodificador

• Secuenciador

Unidad aritmético lógica (ALU):

• Banco de Registros

• CIRcuitos OPeradores

• Registro de Resultados

En algunas ocasiones circuito interno de Reloj

Unidad Central de Procesamiento (CPU)

Registro acumulador.

Registro de estado.

Registros auxiliares.

Registro SP (Stack Pointer) o de pila.

Registro CP (Contador de Programa)

Registros internos.

Acumuladores y Registros del ALUUn registro es una pequeña memoria interna, donde se almacenan temporalmente los resultados de las operaciones. Los registros están formados por biestables colocados de tal forma que pueden almacenar la información en un momento determinado.

La longitud de estos registros viene determinada por el número de biestables que los forman.

Hay cuatro pasos que la mayoría de los CPU usan para su operación: fetch, decode, execute, y writeback.

El primer paso, leer (fetch), implica recuperar una instrucción de la memoria de programa. Un contador de programa (PC), también llamado instruction pointer (IP), indica la ubicación en memoria de la instrucción en turno.

Después de que se lee una instrucción, el Contador de Programa es incrementado por la longitud de la palabra de instrucción en términos de unidades de memoria. Frecuentemente la instrucción, al ser leída de una localidad de memoria relativamente lenta, provoca una pausa en el CPU mientras se completa la transferencia de la instrucción. Este problema en procesadores modernos es corregido en gran parte por el uso de cachés y las arquitecturas en pipeline.

Operación de un CPU [leer]

Hay cuatro pasos que la mayoría de los CPU usan para su operación: fetch, decode, execute, y writeback.

En el paso de decodificación (decode), la instrucción es dividida en partes que tienen significado para otras unidades del CPU.

La manera en que el valor de la instrucción numérica es interpretado está definida por la arquitectura del conjunto de instrucciones del CPU.

Un grupo de números en la instrucción, llamados opcode, indica qué operación realizar.

Las partes restantes de la instrucción proporcionan información requerida, como por ejemplo los operandos para una operación de adición, o una localidad de memoria para re-ubicar algún valor (e.g.: en un registro interno o en una dirección de memoria).

Operación de un CPU [decodificar]

Hay cuatro pasos que la mayoría de los CPU usan para su operación: fetch, decode, execute, y writeback.

En el paso de ejecución (execute) varias unidades del CPU son conectadas de tal manera que la operación pueda ser realizada.

Si, por ejemplo, se trata de una operación de adición, la unidad aritmético lógica (ALU) será conectada al conjunto de registros de entrada y de salida que corresponda. Las entradas proporcionan los valores a ser sumados, y las salidas recibirán el resultado final. La ALU contiene la circuitería para realizar operaciones de aritmética simple y de lógica tales como adición, resta, corrimiento y operaciones booleanas (bitwise).

Los resultados de la operación no solo pueden afectar el contenido del registro de salida sino que pueden modificar los valores de algunos bits del registro de estados o banderas (e.g. overflow, operación cero, ...).

Operación de un CPU [ejecutar]

Hay cuatro pasos que la mayoría de los CPU usan para su operación: fetch, decode, execute, y writeback.

En el paso de escritura (writeback), los resultados del paso de ejecución son transferidos a algún registro de memoria. Ya sea a algún registro interno del CPU para acceso rápido por subsecuentes instrucciones, o a la memoria externa.

Algunos tipos de instrucciones manipulan el contador de programa en lugar producir algún resultado en un registro. Éstas operaciones de "saltos" (jumps) facilitan la implementación de bucles (loops), la ejecución condicional de programas (con el uso de saltos condicionales), y la llamada de funciones dentro de los programas.

Muchas instrucciones también verifican el estado del registro de "banderas" (flags). Estas banderas pueden ser usadas para modificar el flujo del programa.

Operación de un CPU [escritura]

1. Fetch: La Unidad de Control <UC> recibe a través del bus de datos, la instrucción contenida en la localidad de memoria a la que apunta el contador del programa <C> y se transfere al Registro de Instrucciones <RI>.

2. Decode: El Decodier <D> se encarga de interpretarla.

3. El Secuenciador <S> genera la serie de órdenes simples y necesarias para ejecutar la instrucción en el ALU.

4. Execute: El ALU realiza las operaciones indicadas en la instrucción (opcode).

5. Writeback: El resultado de la operación es enviado por la Unidad de Control <UC> al registro de salida en la RAM.

6. El reloj sincroniza el sistema, marcando los instantes en que ha de comenzar cada nueva instrucción.

7. El contador <C> se incrementa apuntando hacia dónde se encuentra la próxima instrucción. Cuando haya terminado de ejecutarse la instrucción en curso, la nueva instrucción pasará al <RI> y se repetirá todo el proceso.

Operación de un CPU Resumen

57

Arquitectura von Neumann

La arquitectura de von Neumann es una familia de arquitecturas que utilizan el mismo bus de direcciones para accesar a tanto dispositivos de almacenamiento de datos como para los de instrucciones. Es decir su mapa de direcciones está compartido, entre los bancos de memoria para ubicar el código y otros para ubicar las variables o datos.

La mayoría de computadoras de escritorio modernas están basadas en esta arquitectura.

Bus de Direcciones

Bus de Control

Bus de Datos e Instrucciones

Memoria Central

Programa y Datos

Memoria Central

Programa y Datos

Memoria RAM

Memoria RAM

Memoria ROM

Memoria ROM

Unidad Central de Procesamiento

(CPU)

Unidad Central de Procesamiento

(CPU)

Origen: Programas pre-cargados

La re-programación de 1ros. ordenadores basados en relevadores/bulbos requería la reestructura y/o re-diseño del sistema.

El proceso era laborioso y requería detallados planes de ingeniería y en ocasiones implicaba la completa re-estructura física del ordenador.

El concepto de programa almacenado revolucionó el diseño ya que un conjunto de instrucciones podían ser almacenadas en memoria, junto con los datos, para ser ejecutadas abriendo la posibilidad de que se pudieran modificar ellos mismos durante la ejecución. (Direccionamiento)

Arquitectura von Neumann

Herramientas de programación como ensambladores y compiladores manejan las instrucciones como datos. Implicación: Se pueden "escribir programas para escribir programas"

Inconvenientes

Compartir el bus de direcciones puede causar la sobre escritura en la sección de memoria asignada para las instrucciones, ya sea por accidente o por mal diseño. En algunos diseños simples, un mal funcionamiento del programa puede dañar otros programas o inclusive el sistema operativo.

En ocasiones pueden llevar a un daño total en el ordenador.

La protección de la memoria y otras formas de control de acceso pueden ayudar a proteger al computado en contra de modificaciones accidentales y/o maliciosas de programas.

La transferencia de datos o instrucciones entre CPU y la memoria es un proceso relativamente lento, lo que genera un cuello de botella (Von Neumann bottleneck). Lo anterior es particularmente importante para el rendimiento del procesador cuando se necesitan procesar grandes cantidades de datos (e.g. DSP). Este problema se redujo introduciendo una memoria caché entre la CPU y la memoria principal, y mejorando los algoritmos de predicción de saltos.

Arquitectura von Neumann

60

Arquitectura Harvard Arquitectura Harvard hacía referencia a las arquitecturas de computadoras que

utilizaban dispositivos de almacenamiento físicamente separados para los datos y para las instrucciones. El término proviene de la computadora Harvard Mark I, que almacenaba las instrucciones en cintas perforadas y los datos en interruptores.

Para aumentar el desempeño en los CPU's tradicionales se incorporaron pequeñas cantidades de memoria muy rápidas (caché) dentro del CPU. En el caso de la arquitectura Harvard se incluyeron dos de ellas, una de datos y otra de instrucciones.

Esta arquitectura suele utilizarse en procesadores digitales de señales (DSP's), usados habitualmente en productos para procesamiento de audio y video.

Bus de Dirección de Datos

Bus de Control

Bus de Datos

Memoria de Datos

Memoria de Datos

Memoria RAM

Memoria RAM

Memoria de InstruccionesMemoria de

Instrucciones

Memoria ROM

Memoria ROM

Bus de Dirección de Instrucciones

Bus de Control

Bus de Instrucciones

Unidad Central de

Procesamiento (CPU)

Unidad Central de

Procesamiento (CPU)

IF DI Ex Wb

IF DI Ex Wb

IF DI Ex Wb

IF DI Ex Wb

IF DI Ex Wb

Manejar datos e instrucciones en buses separados permite un mejor aprovechamiento de los ciclos de reloj, ya que las distintas etapas de operación del procesador pueden concatenarse de manera eslabonada (pipeline)

Una vez que alguna de las etapas de operación (fetch, decode, execute, y writeback) termina, puede continuar su tarea con la información de la siguiente instrucción.

Arquitectura Harvard

IF DI Ex Wb

IF: Instruction FetchDI: Decode InstructionEx: ExecuteWb: Write-back

0 1 2 3 4 5 6 7 8

CPU cycles

@i@i+1

@i@i+1@i+2@i+3

63

CISC (Complex instruction set computing)

El modelo de arquitectura de computadora CISC de conjunto de instrucciones complejo, se caracteriza por tener muchas instrucciones y permitir en operaciones individuales operaciones complejas entre datos situados en la memoria y/o en los registros internos.

Este tipo de arquitectura busca conseguir un aumento de prestaciones con base en el incremento de la complejidad de las instrucciones.

Los CISC pertenecen a la primera corriente de construcción de procesadores. Ejemplos de ellos son: Motorola 68000, Zilog Z80 y toda la familia Intel x86. Los procesadores CISC dominan el mercado de los ordenadores personales, debido a su popularidad y al aumento constante en su capacidad de procesamiento (e.g. x86).

64

CISC (Complex instruction set computing)

Historia: En los años setenta los procesadores eran eran diseñados considerando las limitaciones en la transferencia de datos entre el procesador y la memoria. Bajo esa óptica, no tenía mucho sentido el hacer procesadores más rápidos si la velocidad de acceso estaba acotada por la tecnología de las propias memorias.

Los registros eran difíciles y costosos de implementar debido a sus inter-conexiones.

Mínimo número de registros o registros enfocados a tareas específicas Tenía sentido diseñar procesadores que minimizaran la transferencia

de información a las localidades de memoria se realizara sin intermediarios.

Los diseñadores se enfocaron en crear conjuntos de instrucciones específicas para cada posible operación o combinación de entrada/salida de registros o memoria.

65

CISC (Complex instruction set computing)

Historia (cont.): La meta era proveer cada posible modo de direccionamiento (combinación de registros) para cada instrucción. Un principio conocido como ortogonalidad. Esto condujo a un CPU complejo, pero en teoría capaz de configurar cada posible orden individualmente, haciendo la ejecución más rápida en comparación del uso de un grupo de órdenes simples.

Ya que un set de instrucciones complejo como el CISC dificulta la ejecución de operaciones en paralelo, en la actualidad la mayoría de los sistemas CISC de alto rendimiento implementan un sistema de conversión de instrucciones complejas en conjuntos de instrucciones simples (como las del tipo usado en los procesadores RISC), llamadas microinstrucciones.

67

SISC (Simple Instruction Set Computing)

Es un tipo de arquitectura de microprocesadores orientada al procesamiento de tareas en paralelo la cual aprovecha las tecnologías de fabricación VLSI, con lo que se permite integrar múltiples dispositivos de bajo costo en una sóla pastilla.

La arquitectura RISC es un subconjunto del SISC, centrada en la velocidad de procesamiento gracias al empleo de un conjunto pequeño de instrucciones.

68

RISC (Reduced instruction set computing)

La arquitectura RISC es un diseño de CPU que está basado en conjuntos de instrucciones simples, con muy pocos modos de direccionamiento, lo que posibilita el paralelismo y la segmentación de rutinas.

Los diseños RISC tienden a utilizar un modelo de arquitectura Harvard, donde los buses de instrucciones y datos están separados, lo mejora el rendimiento, al permitir el acceso a los cachés de datos e instrucciones de manera independiente.

Su funcionamiento simple los hace idóneos para aplicaciones de bajo consumo de energía o de tamaño limitado, además permite su fabricación en líneas de producción poco sofisticadas (lo que permite la re-utilización de líneas de producción).

70

RISC (Reduced instruction set computing)

Objetivos del desarrollo de los RISC:– Velocidad: Un número pequeño de instrucciones (opcode) permite

describirlas con pocos bits, dejando espacio dentro de la propia palabra o instrucción para incluir en ella datos o constantes, reduciéndose el número de accesos a registros o memoria para completar la información.

– Paralelismo: Instrucciones de longitud fija hace que las instrucciones (opcodes) y operandos siempre estén ubicados en los mismos campos de bits, alineados dentro de los límites de la unidad lógica binaria del procesador (word boundaries), lo que facilita el uso de pipelines (VHDL).

– Simplicidad: Modos de direccionamiento sencillos permiten definir un conjunto de registros casi homogéneo con sólo algunos de ellos dedicados a las operaciones de escritura/lectura con la memoria externa, lo que facilita el diseño de la interfaz de memoria y simplifican el diseño del procesador.

73

Características RISC

Conjunto de instrucciones Load/Store (Cargar/Almacenar): Sólo estas instrucciones permiten el acceso a la memoria; las demás operaciones utilizan el conjunto de registros para almacenar los resultados. Lo anterior simplifica el direccionamiento y acorta los tiempos de acceso del CPU. También se facilita la recuperación de fallos en paginas (page faults) cuando se emplea algún esquema de memoria virtual.

Arquitectura no destructiva de tres direcciones: Los procesadores CISC destruyen la información que existe en alguno de los registros durante la ejecución normal de instrucciones. Las instrucciones RISC (de tres direcciones) contienen dos campos para operandos y uno independiente para el resultado. Esta arquitectura "no destructiva" permite a los compiladores organizar las instrucciones de modo que mantengan llenos los conductos (pipelines) del chip, y por tanto reutilizar los operandos optimizando la concurrencia.

74

Características RISC Ausencia de microcódigo: A diferencia de los procesadores CISC donde el

uso de microcódigo, obliga al hardware a interpretar cada instrucción de manera dinámica (impidiendo también la implementación de instrucciones de ciclos único); en los procesadores RISC las funciones y el control de registros están implementados por hardware (hardwired) con lo que se obtienen una máxima velocidad y eficiencia.

Ejecución en conductos (pipelined): El tamaño predeterminado de las instrucciones RISC permite que las distintas etapas del ciclo de operación del CPU (fetch, decoding, execution y result write-back) puedan realizarse en paralelo conforme el contador de programa avanza en el código.

Ejecución en ciclos únicos (single-cycle): Algunas instrucciones puede ser ejecutadas en un único ciclo de la CPU. La ejecución en ciclos únicos también simplifica la gestión de las interrupciones y de pipelines.

76

Multiproceso Tradicionalmente se ha tratado de mejorar las prestaciones de un procesador

aumentando su velocidad, sin embargo es posible construir sistemas, que aún teniendo procesadores "lentos", ofrezcan prestaciones significativamente superiores.

Un conjunto de tareas puede ser completado mas rápidamente si varias unidades ejecutan en paralelo un determinado proceso. Los sistemas multi-procesador lo hacen al incorporan varios procesadores en la misma pastilla.

El proceso de dividir la ejecución de su código entre varios procesadores se le conoce como multi-enhebrado (multithreading). Para lograrlo, se requiere conocer no sólo como están interconectados dichos procesadores, y la forma en que el código que se ejecuta en los mismos; sino que es necesario modificar varias facetas del sistema operativo, como la manera en la que se organiza el código y los datos, así como la manera en que operan de los propios lenguajes de programación.

77

Clasificación de los sist. procesadores

– SISD o secuencia única de instrucciones y datos (Single Instruction, Single Data): una sola secuencia de instrucciones opera sobre una sola secuencia de datos (caso típico de los ordenadores personales).

– SIMD o secuencia única de instrucciones y múltiple de datos (Single Instruction, Multiple Data): una sola secuencia de instrucciones opera, simultáneamente, sobre múltiples secuencias de datos (array processors).

– MISD o múltiples secuencias de instrucciones y única de datos (Multiple Instruction, Single Data): múltiples secuencias de instrucciones operan, simultáneamente, sobre una sola secuencia de datos (sin implementaciones útiles actualmente).

– MIMD o múltiples secuencias de instrucciones y datos (Multiple Instruction, Multiple Data): múltiples secuencias de instrucciones operan, simultáneamente, sobre múltiples secuencias de datos.

78

Multiproceso

La mayoría de los sistemas multiprocesadores entran en la categoría de sistemas MIMD. Ello implica que son máquinas con múltiples nodos de proceso autónomos, cada uno de los cuales opera sobre su propio conjunto de datos. Todos los nodos son idénticos en funciones, por lo que cada uno puede operar en cualquier tarea o porción de la misma.

Este sería el caso donde en lugar de subdividir a un solo microprocesador, se incorpora un segundo microprocesador, idéntico al primero. El inconveniente es que la RAM debía de ser tratada a nivel hardware y los módulos diseñados para plataformas monoprocesador no son compatibles o no funcionan con la misma eficiencia, que para las plataformas multiprocesador.

Al tener dos microprocesadores separados, ambos usaran registros de manera independiente, con sus propios accesos asíncronos a la memoria. En estas plataformas, la relación de RAM por procesador es de 1/1.

79

Multiproceso: Configuración de memorias

Multiprocesadores de memoria distribuida (distributed-memory multiprocessors), también denominados como multiprocesadores vagamente acoplados (loosely coupled).

– Se caracterizan porque cada procesador sólo puede acceder a su propia memoria.

– Se requiere comunicación entre los procesadores para coordinar las operaciones y mover los datos.

– Los datos pueden ser intercambiados, pero no pueden ser compartidos.

– Dado que los procesadores no comparten un espacio de direcciones común, no hay problemas asociados con tener múltiples copias de los datos (no existe la competencia por recursos), pero pueden ocurrir problemas de sincronía.

– Además de la complejidad de las interconexiones, una de las principales desventajas de estos sistemas, como es evidente, es la duplicación de recursos caros como memoria, dispositivos de entrada/salida, que además están desocupados en gran parte del tiempo.

Memoria 1Memoria 1

CPU 1CPU 1

E/S Typ1E/S Typ1

CPU 2CPU 2

Memoria 2Memoria 2

Bus de Interconexión

E/S Typ2E/S Typ2

E/S Typ3E/S Typ3

E/S Typ1E/S Typ1

E/S Typ2E/S Typ2

E/S Typ3E/S Typ3

80

Multiproceso: Configuración de memorias

Multiprocesadores de memoria compartida (shared-memory multiprocessors), también conocidos como multi-procesadores estrechamente acoplados (tightly coupled multiprocessors).

– Son sistemas con múltiples procesadores que comparten un único espacio de direcciones de memoria.

– Cualquier procesador puede acceder a los mismos datos, al igual que puede acceder a ellos cualquier dispositivo de entrada/salida.

– El sistema de interconexión más empleado para estos casos, es el de bus compartido (shared-bus). Lo que tiene el inconveniente de limitar las prestaciones del sistema a medida nuevos procesadores son incorporados.

– La razón es la saturación del bus, es la lucha entre los diferentes dispositivos y procesadores para obtener el control del bus, y hacer uso de el tanto para transferir datos como instrucciones.

MemoriaMemoria

Bus de Interconexióncompartido

(shared-bus)

E/S Typ1E/S Typ1

E/S Typ2E/S Typ2

E/S Typ3E/S Typ3

CPU 1CPU 1

CPU 2CPU 2

CPU 3CPU 3

81

Multiproceso: Configuración de memorias

Es evidente, que los sistemas actuales tienden al uso de arquitecturas de memoria compartida, fundamentalmente por razones de costos, a pesar del problema de la competencia por el bus.

Los principales responsables de dicha disputa son:• La memoria (cada CPU debe usar el bus para acceder a la

memoria principal), • La comunicación (el bus es usado por los "bus masters" para la

comunicación y coordinación)• Y la latencia de la memoria (el subsistema de memoria mantiene al

bus durante las transferencias de datos, y en función de la velocidad a la que la memoria puede responder a las peticiones, puede llegar a ser un factor muy significativo).

83

Multitarea en procesadores CISC La multitarea en la arquitectura CISC tradicional nunca ha sido real, tal como

en los RISC sí lo es. La cantidad de instrucciones complejas y diferentes, evita la subdivisión de tareas, al menos a nivel lógico. Por lo tanto, la multitarea es aparente y ejecutada en orden de prioridad.

Debido a lo redundante de las microinstrucciones, los sistemas operativos

diseñados para los procesadores CISC, contemplan la subdivisión del procesador físico en varios virtuales, y procuran la reducción del número de instrucciones redundantes por cada una de las instancias.

Con una arquitectura del software optimizada, se puede paginar la memoria RAM de manera dinámica, asignando una cantidad suficiente de bytes para cada tarea en ejecución. En cada ciclo de reloj se procesa alguna de las tareas instanciadas y pendientes de ser atendidas. Para determinar el orden de ejecución se usan colas de atención tipo FIFO para el procesamiento de datos, y tipo LIFO para el manejo de las interrupciones.

84

Multitarea en procesadores CISC

Los microprocesadores actuales, al ser híbridos, permiten cierta parte de multitarea real. La tarea en ejecución (en foco del usuario) es procesada como en un CISC tradicional, mientras que las tareas pendientes, dependiendo del tiempo de inactividad, son procesadas por el sistema como tareas de bajo nivel, en donde sus instrucciones se ejecutan (después de una conversió o traducción) en modo RISC.

Debido a que el usuario puede enfocarse en una sola tarea a la vez, el resto de tareas que deja pendientes y que no son compatibles con el modelo de traducción CISC/RISC, pasan a ser atendidas por el pipeline tradicional CISC.

De igual manera si se trata de tareas de bajo nivel, tal como tareas gráficas o tareas de cálculo matemático intensivo, defragmentaciones de disco, chequeo de la integridad de la información, formateo, etc. son atendidas también en modo CISC.