ISI374 – Arquitectura de Computadores Clase 18: Jerarquía de memoria Pt.1 Departamento de...

-

Upload

angeles-montes-maidana -

Category

Documents

-

view

213 -

download

0

Transcript of ISI374 – Arquitectura de Computadores Clase 18: Jerarquía de memoria Pt.1 Departamento de...

ISI374 – Arquitectura de ComputadoresClase 18: Jerarquía de memoria Pt.1

Departamento de Ingeniería de SistemasUniversidad de Antioquia

2010-1

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

2

Resumen

Modelo de von Neumann Características de los sistemas de memoria Memorias semiconductoras Almacenamiento en el computador Brecha de rendimiento entre el procesador y la memoria Principio de localidad Jerarquía de memoria Aspectos básicos de memoria cache

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Modelo de von Neumann

Concepto del programa almacenado Las instrucciones y los datos de un programa se guardan en una

memoria de lectura/escritura

3

CPU

Busses

Controllers

Working storageSRAM (Cache)DRAM (Main

memory)

Permanent storageMagnetic disks

Optical disksTapes

InputKeyboard

MouseScanner

Digital CameraNetwork

Sound, Video cards

ScreenPrinter

Output Mem

ory

syst

em

I/O

syst

em

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Características de los sistemas de memoria

Ubicación (Interna, Externa)

Capacidad

Unidad de transferencia

Método de acceso (Secuencial, Directo, Aleatorio, Asociativo)

Rendimiento (Tiempo de acceso (latencia), Tiempo de ciclo de memoria, Tasa de transferencia)

Tecnología de fabricación (Semiconductor (Transistores CMOS), Superficie magnética, Óptica)

Características físicas (Volátil, No volátil)

4

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Memorias semiconductoras

Memoria de acceso aleatorio (RAM) Memoria volátil Lectura/escritura El tiempo de acceso es independiente de la posición de memoria y

de la secuencia previa de accesos La memoria RAM es la memoria a la que se refieren las

características de un computador Almacena las instrucciones y los datos que requiere el computador

para ejecutar los programas» 1981: “640KB of memory ought to be enough for anybody”

Bill Gates» 2007: Windows Vista requiere mínimo de 2GB de RAM para

comportarse decentemente!!!

5

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Memorias semiconductoras

Dynamic RAM (DRAM) Es la forma más popular de RAM Construcción basada en celdas que almacenan el dato como la

carga de un capacitor (es, en esencia, un dispositivo analógico) La presencia o ausencia de carga se interpreta como un estado

binario (0, 1) Requiere de un refrescamiento periódico de la carga para conservar

el dato almacenado Gran densidad de integración (1 transistor por celda) y bajo costo

6

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Memorias semiconductoras

Static RAM (SRAM) Dispositivo digital que usa la misma tecnología de fabricación de la

CPU Se emplea para ofrecer una interfaz directa a la CPU (memoria

cache) Una celda SRAM consiste en un flip-flop biestable: cuando no se

direcciona la celda, los dos transistores de acceso están abiertos y el dato se conserva en un estado estable

El flip-flop necesita de un suministro eléctrico constante para conservar la información (volátil)

No es necesario un ciclo de refrescamiento SRAM es más rápida, menos densa (6 transistores por celda),

consume más potencia que DRAM, y es mucho más costosa

7

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Almacenamiento en el computador

Static RAM (SRAM) 0.5ns – 2.5ns, USD $2000 – $5000 por GB

Dynamic RAM (DRAM) 50ns – 70ns, USD $20 – $75 por GB

Disco magnético 5ms – 20ms, USD $0.20 – $2 por GB

Memoria ideal Tiempo de acceso de SRAM Capacidad y costo/GB del disco

8

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Brecha de rendimiento entre el procesador y la memoria

9

P: 50%/year

DRAM: 10%/year

Processor-Memoryperformance gap(grows ~40%/year)

Ley de Moore

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Acerca del sistema de memoria10

Hechos: Es necesario suministrar al procesador una instrucción y algunos

operandos cada nuevo ciclo de reloj Las memorias grandes son lentas, y las memorias rápidas son

pequeñas

¿Cómo crear una memoria que ofrezca la ilusión de ser grande, barata y rápida (la mayor parte del tiempo)?

Con una jerarquía Con paralelismo

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Principio de localidad11

En un momento dado, un programa sólo accede a una pequeña porción de su espacio de direcciones

Localidad temporal Es muy probable que los ítems a los que se ha accedido

recientemente sean referenciados pronto otra vez Ejemplo: las instrucciones de un bucle

Mantener los ítems accedidos más recientemente cerca del procesador

Localidad espacial Es muy probable que los ítems cercanos a aquellos accedidos

recientemente sean referenciados pronto Ejemplos: acceso secuencial a instrucciones, elementos de un array

Mover bloques consistentes en varias palabras contiguas cerca del procesador

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

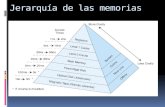

Jerarquía de memoria12

Sacando provecho del principio de localidad se puede tener la ilusión de disponer de tanta memoria como lo permite la tecnología más barata, a la velocidad de la tecnología más rápida

Jerarquía de memoria

Consiste en disponer de diferentes niveles de memoria con diferentes velocidades y tamaños

Almacenar todo en el disco Copiar los ítems accedidos recientemente (y sus vecinos) desde el

disco a una memoria DRAM más pequeña» Memoria principal

Copiar los ítems accedidos recientemente (y sus vecinos) desde la DRAM a una memoria SRAM más pequeña

» Memoria caché unida a la CPU

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Memoria cache ($ memory)13

Nivel de la jerarquía de memoria que ubicado entre el procesador y la memoria principal

Se implementa usando la misma tecnología de fabricación de la CPU (normalmente integrada en el mismo chip)

Más rápida pero también más costosa que la DRAM

La memoria cache almacena un subconjunto de la memoria principal

La mayoría de los procesadores poseen caches de datos e instrucciones separadas

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

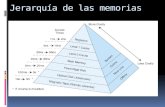

Representación de la jerarquía de memoria14

Procesador

Tamaño de memoria en cada nivel

Mayor distancia al procesador, mayor tiempo de acceso

Nivel 1Nivel 2

Nivel n

Nivel 3. . .

Mayor

Menor

Niveles en la jerarquía de memoria

En niveles inferiores, la latencia crece y el precio por bit disminuye

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Terminología de la jerarquía de memoria15

Bloque: Unidad de información que está presente o

no en un nivel de la jerarquía Unidad mínima de transferencia

» Puede ser de varias palabras Cuando el procesador solicita un dato:

Si el dato accedido está en el nivel superior:

» Acierto (Hit): acceso satisfecho por el nivel superior

Tasa de aciertos (Hit ratio): aciertos/accesos

Tiempo de acierto (Hit time) Si el dato accedido no está en el nivel

superior:» Fallo (Miss): el bloque es copiado desde el

nivel inferior Tiempo necesario: penalización de fallo

(miss penalty) Tasa de fallos (Miss ratio): fallos/accesos

= 1 – tasa de aciertos

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Tiempo de acierto, penalización de fallo16

Hit time: Tiempo de acierto Tiempo para acceder a un nivel de la jerarquía Consiste en:

» Tiempo para acceder al bloque + Tiempo para determinar si hay acierto/fallo

Miss Penalty: Penalización de fallo Tiempo para reemplazar un bloque en un nivel de la jerarquía con el

bloque correspondiente del nivel inferior Consiste en:

» Tiempo para acceder al bloque en el nivel inferior +Tiempo para transferir ese bloque al nivel que sufrió el fallo +Tiempo para insertar el bloque en este nivel +Tiempo para pasar el bloque a quien lo solicita

Para la que el diseño de la jerarquía de memoria tenga sentido:Hit Time << Miss Penalty

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

¿Cómo se gestiona la jerarquía?17

Registros Memoria Por el compilador (programador?)

Memoria cache Memoria principal Por el hardware controlador de la memoria cache

Memoria principal Discos Por el sistema operativo (Memoria virtual)

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Aspectos básicos de memoria cache18

Dos cuestiones a responder (en hardware): P1: ¿Cómo sabemos si un dato está o no en la cache? P2: Si está, ¿cómo encontrarlo?

Cache de emplazamiento directo (Direct-mapped cache) Cada posición de memoria se mapea a un solo bloque en la

cache (sólo hay una opción) Varios bloques del nivel inferior deben compartir bloques en la

cache

Mapeo entre direcciones y posiciones de cache (para responder P2)

(Dirección del bloque) mod (# bloques en la cache)

Si el # bloques en la cache es una potencia de 2, se emplean los log2(# bloques) bits inferiores de la dirección para acceder a la cache

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Aspectos básicos de memoria cache19

Cache de emplazamiento directo (Direct-mapped cache)

(Dirección del bloque) mod (# bloques en la cache)

Tamaño de bloque: 1 palabra (32 bits)# bloques = 8 Se emplean log2(8) = 3 bits de la dirección del bloque para acceder a la cache (Index)

XX XX XX XX XX XX XX XX

Bloques de una palabra: los dos bits inferiores definen el byte dentro de la palabra

Index

XX: bits que se ignoran cuando se hace referencia al bloque

Diferentes bloques de memoria mapean al mismo bloque en la cache

Dirección del bloque

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Tags y bit de validez20

Si varios bloques del nivel inferior pueden ocupar el mismo bloque en la cache, ¿cómo sabemos cuál dato en particular está almacenado en una posición de la cache?

Disponer de un tag asociado con cada bloque de la cache, que contiene información de la dirección (la parte superior de la misma) necesaria para identificar el bloque (para responder P1)

¿Cómo sabemos si el bloque de cache contiene información válida?

Por ejemplo, cuando arranca el procesador, la cache no tiene información útil y su contenido no tiene significado alguno

Bit de validez: 1 = Dato válido (presente), 0 = Dato inválido (no presente)

Inicialmente en 0

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

Ejemplo de acceso a la cache21

Cache de emplazamiento directo (direct-mapped cache) de 8 bloques, 1 palabra/bloque

Ilustrar el comportamiento de la cache ante la siguiente secuencia de accesos a bloques en memoria:22, 26, 22, 26, 16, 3, 16, 18 (direcciones de palabra)

# bloques = 8 = 23 3 bits inferiores de la dirección para acceder a la cache

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

22

Ejemplo de acceso a la cache

Estado inicial de la memoria cache

Index V Tag Data

000 N

001 N

010 N

011 N

100 N

101 N

110 N

111 N

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

23

Ejemplo de acceso a la cache

Index V Tag Data

000 N

001 N

010 N

011 N

100 N

101 N

110 N

111 N

Word addr Binary addr Hit/miss Cache block

22 10 110 Miss 110

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

24

Ejemplo de acceso a la cache

Index V Tag Data

000 N

001 N

010 N

011 N

100 N

101 N

110 Y 10 Mem[10110]

111 N

Word addr Binary addr Hit/miss Cache block

22 10 110 Miss 110

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

25

Ejemplo de acceso a la cache

Index V Tag Data

000 N

001 N

010 Y 11 Mem[11010]

011 N

100 N

101 N

110 Y 10 Mem[10110]

111 N

Word addr Binary addr Hit/miss Cache block

26 11 010 Miss 010

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

26

Ejemplo de acceso a la cache

Index V Tag Data

000 N

001 N

010 Y 11 Mem[11010]

011 N

100 N

101 N

110 Y 10 Mem[10110]

111 N

Word addr Binary addr Hit/miss Cache block

22 10 110 Hit 110

26 11 010 Hit 010

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

27

Ejemplo de acceso a la cache

Index V Tag Data

000 Y 10 Mem[10000]

001 N

010 Y 11 Mem[11010]

011 Y 00 Mem[00011]

100 N

101 N

110 Y 10 Mem[10110]

111 N

Word addr Binary addr Hit/miss Cache block

16 10 000 Miss 000

3 00 011 Miss 011

16 10 000 Hit 000

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

28

Ejemplo de acceso a la cache

Hits = 3, Misses = 5, Hit rate = 3/8 (37.5%), Miss rate = 5 / 8 (62.5%)

Index V Tag Data

000 Y 10 Mem[10000]

001 N

010 Y 10 Mem[10010]

011 Y 00 Mem[00011]

100 N

101 N

110 Y 10 Mem[10110]

111 N

Word addr Binary addr Hit/miss Cache block

18 10 010 Miss 010

ISI3

74 -

Arqu

itect

ura

de C

ompu

tado

res

(201

0-1)

29

Lecturas recomendadas

Computer organization and architecture. Designing for performance, 6th ed., Chapter 5. W. Stallings. Pearson Education

N. Mahapatra and B. Venkatrao. The Processor-Memory bottleneck: Problems and Solutions. Crossroads, The ACM Student Magazine, V. 5, N. 3, Spring 1999.Accesible vía web: http://doi.acm.org/10.1145/357783.331677

Computer organization and design. The hardware/software interface, 3rd ed., Chapter 7. D. Patterson and J. Hennessy. Morgan Kaufmann Publishers