procesamientoParalelo

-

Upload

vladimir-ft -

Category

Documents

-

view

213 -

download

0

Transcript of procesamientoParalelo

-

8/22/2019 procesamientoParalelo

1/65

Procesamiento

Paralelo

Basado en: Stallings. Computer Organization and Architecture. Design for performance. 6ed

-

8/22/2019 procesamientoParalelo

2/65

Antecedentes

Limitaciones de las arquitecturas tradicionales

Limitaciones de la tecnologia subyascente

Agotamiento de la arquitectura secuencial

Necesidad de mayor capacidad deprocesamiento

-

8/22/2019 procesamientoParalelo

3/65

Clasificacion de Flynn

Single instruction, single data stream - SISD

Single instruction, multiple data stream - SIMD

Multiple instruction, single data stream - MISD

Multiple instruction, multiple data stream -MIMD

-

8/22/2019 procesamientoParalelo

4/65

Single Instruction, Single Data Stream -

SISD

Procesador nico

Flujo de instrucciones nico

Datos almacenados en una memoria nica

Uni -procesador

-

8/22/2019 procesamientoParalelo

5/65

Single Instruction, Multiple Data Stream

- SIMD

Instruccion de mquina nica Controla la ejecucin simultnea

Varios elementos de procesamiento

-

8/22/2019 procesamientoParalelo

6/65

Single Instruction, Multiple Data Stream

- SIMD

Cada elemento procesador tiene asociada una unidad de memoria

Cada instruccin es ejecutada sobre un conjunto de datos diferentepor diferentes procesadores

Procesadores vectoriales y matriciales

-

8/22/2019 procesamientoParalelo

7/65

Multiple Instruction, Single Data Stream

- MISD

Secuencia de datos

Emitidos a un conjunto de procesadores

Cada procesador ejecuta una secuencia deinstrucciones diferente

Nunca se ha implementado

-

8/22/2019 procesamientoParalelo

8/65

Multiple Instruction, Multiple Data

Stream- MIMD

Conjunto de procesadores

Ejecutan simultneamente diferentes secuencias deinstrucciones

Diferentes conjuntos de datos

SMPs, clusters y sistemas NUMA

-

8/22/2019 procesamientoParalelo

9/65

Taxonomia de Arquitectura de

Procesadores Paralelos

-

8/22/2019 procesamientoParalelo

10/65

MIMD - Repaso

Procesadores de propsito general

Cada uno puede ejecutar todas las instrucciones

necesarias Se pueden clasificar por el mtodo de

comunicacin entre procesadores:Fuertemente acoplados.

Debilmente acoplados.

-

8/22/2019 procesamientoParalelo

11/65

Organizaciones Paralelas - MIMD

Memoria Compartida

-

8/22/2019 procesamientoParalelo

12/65

SMP Fuertemente acoplados

Los procesadores comparten memoria Se comunican mediante la memoria compartida

Symmetric Multiprocessor (SMP)Comparten una unica

memoria

Bus compartido paraacceder a memoria

El tiempo de acceso acualquier area de memoriaes aproximadamente elmismo para cualquierprocesador

-

8/22/2019 procesamientoParalelo

13/65

NUMA Fuertemente Acoplados

Acceso a memoria no uniforme Los tiempos de acceso a diferentes regiones de

memoria puede diferir

-

8/22/2019 procesamientoParalelo

14/65

Organizaciones Paralelas - MIMD

Memoria Distribuida

-

8/22/2019 procesamientoParalelo

15/65

Clusters Debilmente Acoplados

Coleccin de procesadores independientes o SMP Interconectados para formar un cluster

Comunicacin via rutas fijas o conexiones de red

-

8/22/2019 procesamientoParalelo

16/65

Multiprocesadores Simetricos

Un computador autonomo con las sgtes. caractersticasDos o mas procesadores de capacidad comparableLos procesadores comparten la misma memoria y E/S

Los procesadores se conectan mediante un bus u otro tipo deconexin interna

El tiempo de acceso a memoria es aproximadamente el mismopara cada procesador

Todos los procesadores comparten el acceso a E/S

Sea mediante los mismos canales o canales diferentes quepermitan acceso a los dispositivos

Todos los procesadores pueden realizar las mismas funciones(de ah la simetra)

Sistema controlado por un sistema operativo integrado

Proporciona interaccin entre procesadores

Interaccin a nivel de elementos de trabajo, tarea, archivos y datos

-

8/22/2019 procesamientoParalelo

17/65

Ventajas SMP

RendimientoSi algun trabajo puede hacerse en paralelo

DisponibilidadPuesto que todos los CPU pueden realizar las mismas

funciones, la falla de un CPU no detiene el sistema Crecimiento incremental

El usuario puede mejorar el rendimiento agregandoCPUs adicionales

EscalamientoLos vendedores pueden ofrecer un rango de

productos basados en el nmero de CPUs

-

8/22/2019 procesamientoParalelo

18/65

Diagrama de bloques de un

multiprocesador fuertemente acoplado

-

8/22/2019 procesamientoParalelo

19/65

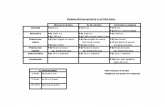

Clasificacin de organizacin

Bus comn o de tiempo compartido

Memoria multipuerto

Unidad de control central

-

8/22/2019 procesamientoParalelo

20/65

Bus de Tiempo Compartido

El mtodo mas sencillo

Estructura e interfaz similar a un sistema de unsolo CPU

Ofrece las siguientes caractersticas

Direccionamiento distingue mdulos en el busArbitraje cualquier mdulo puede ser maestro

temporalmente

Tiempo compartido si un mdulo tiene el bus, otros

deben esperar y pueden tener que suspenderse En la actualidad tienen multiples CPUs asi como

mltiples mdulos de E/S

-

8/22/2019 procesamientoParalelo

21/65

Bus Compartido

-

8/22/2019 procesamientoParalelo

22/65

Bus de Tiempo Compartido

VentajasSimplicidad

Flexibilidad

Fiabilidad

Desventajas

Rendimiento limitado por eltiempo de ciclo del bus

Cada procesador debe tenercache localReduce el nmero de accesos

al bus

Conduce a problemas decoherencia cacheResuelto en hardware

-

8/22/2019 procesamientoParalelo

23/65

Redes de interconexion

Switch de barra cruzadaArquitectura no bloqueante

La red es de orden O(N2)

-

8/22/2019 procesamientoParalelo

24/65

Redes de interconexion

Red omegaRequiere log2N etapas para conectar N CPUs y N

memorias, con N/2 switches por etapa

Es bloqueante

-

8/22/2019 procesamientoParalelo

25/65

Redes de interconexion

Red BenesRequiere 2log2N 1 etapas para conectar N CPUs y N

memorias, con N/2 switches por etapa

No bloqueante

-

8/22/2019 procesamientoParalelo

26/65

Redes de interconexion

Red BanyanRequiere (N/2)log2N elementos para conectar N CPUs

y N memorias

Bloqueante

-

8/22/2019 procesamientoParalelo

27/65

Memoria Multipuerto

Acceso directo independiente de mdulos de memoriapor cada CPU

Se requiere de lgica para resolver conflictos

Ninguna o poca modificacin de los CPUs o mdulos

requerida

M i M lti t V t j

-

8/22/2019 procesamientoParalelo

28/65

Memoria Multipuerto Ventajas y

Desventajas

Mas complejaAcceso extra en sistema de memoria

Mejor rendimientoCada procesador tiene una ruta dedicada a cada

mdulo

Se puede configurar partes de la memoria comoprivadas para uno o mas procesadores

Seguridad mejorada Politica de actualizacin de cache escritura

directa

-

8/22/2019 procesamientoParalelo

29/65

Unidad de Control Central

Flujos de datos separados por canales entre

mdulos independientes

Se puede encolar requerimientos

Realiza arbitraje y temporizacin

Transferir estado y control Realiza alertas de actualizacin de cache

Las interfaces con los mdulos se mantienen

iguales e.g. IBM S/370

-

8/22/2019 procesamientoParalelo

30/65

Consideraciones del Sistema Operativo

Procesos concurrentes simultneos Planificacin

Sincronizacin

Administracin de memoria Fiabilidad y tolerancia a fallos

-

8/22/2019 procesamientoParalelo

31/65

IBM S/390 Mainframe SMP

-

8/22/2019 procesamientoParalelo

32/65

S/390 Componentes Crticos

Unidad de procesamiento (PU)Microprocesador CISC

Las instrucciones frecuentemente utilizadas soncableadas

Cache L1 de 64K unificada con tiempo de acceso de1 ciclo

Cache L2384k

Adaptador Bus Switching Network (BSN)Incluye 2M of cache L3

Tarjeta de memoria card8G por tarjeta

-

8/22/2019 procesamientoParalelo

33/65

Coherencia Cache y Protocolo MESI

Problema multiples copias del mismo dato endiferentes caches

Puede resultar en una vision inconsistente de lamemoria

La politica de post-escritura puede conducir ainconsistencias

La post-escritura puede tambien ocasionar

problemas a menos que las cache monitoreen eltrafico de memoria

-

8/22/2019 procesamientoParalelo

34/65

Soluciones Software

El problema es resuelto por el compilador y el sistemaoperativo

La sobrecarga se transfiere al tiempo de compilacin

La complejidad de diseo se transfiere del hardware al

software Sin embargo, el software tiende a tomar decisiones

conservadorasUtilizacion ineficiente de cache

Analizar el codigo para determinar periodos seguros paraponer en cache variables compartidas

-

8/22/2019 procesamientoParalelo

35/65

Soluciones Hardware

Protocolos de coherencia Cache

Reconocimiento dinamico de problemaspotenciales

Tiempo de ejecucion Uso mas eficiente de cache

Transparente para el programador

Protocolos de directorio Protocolos Snoopy

-

8/22/2019 procesamientoParalelo

36/65

Protocolos de Directorio

Recolecta y mantiene informacion sobre copiasde datos en cache

El directorio se almacena en memoria principal

Los requerimientos se verifican contra eldirectorio

Se realizan transferencias apropiadas

Crea un cuello de botella central

Efectivo en sistemas de gran escala conesquemas de interconexion complejos

-

8/22/2019 procesamientoParalelo

37/65

Protocolo Snoopy

Se distribuye la responsabilidad de la coherenciacache entre los controladores de cache

La cache reconoce que una linea esta

compartida Las actualizaciones se anuncian a otras caches

Adecuado para multiprocesadores basados enbus

Incrementa el trafico en el bus

-

8/22/2019 procesamientoParalelo

38/65

Invalidacion de Escritura

Multiples lectores, un escritor Cuando se requiere una escritura, todas las demas

caches de la linea se invalidan

El proceso escritor entonces tiene acceso exclusivo

hasta que la linea es requerida por otro procesador Se usa en sistemas Pentium II y PowerPC

El estado de cada linea se marca como modificado,exclusivo, compartido o invalido

MESI

-

8/22/2019 procesamientoParalelo

39/65

Actualizacion de Escritura

Multiples lectores y escritores La palabra actualizada se distribuye a todos los

demas procesadores

Algunos sistemas utilizan una mezcla adaptivade ambas soluciones

Diagrama de Transiciones de Estado

-

8/22/2019 procesamientoParalelo

40/65

Diagrama de Transiciones de Estado

MESI

-

8/22/2019 procesamientoParalelo

41/65

Clusters

Alternativa a SMP Alto rendimiento

Alta disponibilidad

Aplicaciones servidor

Un grupo de computadores autnomos

interconectados Trabajan juntos como un recurso unificado

Ilusin de ser un computador

Cada computador se denomina un nodo

-

8/22/2019 procesamientoParalelo

42/65

Beneficios de los Cluster

Escalabilidad absoluta

Escalabilidad incremental

Alta disponibilidad Relacion costo/rendimiento superior

Configuraciones de Clusters - Standby

-

8/22/2019 procesamientoParalelo

43/65

Configuraciones de Clusters - Standby

Server, No Shared Disk

Configuraciones de Cluster -

-

8/22/2019 procesamientoParalelo

44/65

Configuraciones de Cluster -

Disco Compartido

Aspectos de diseo de Sistemas

-

8/22/2019 procesamientoParalelo

45/65

Aspectos de diseo de Sistemas

Operativos para clusters

Gestion de fallos

Alta disponibilidadTolerancia a fallos

Failover Conmutando aplicaciones y datos de un sistema caido a otro

alternativo dentro del cluster

Failback Restauracion de aplicaciones y datos al sistema original

Despues que se arreglo el problema

Balanceo de cargaEscalabilidad incremental

Automaticamente incluye nuevos computadores en laplanificacin

El middleware debe reconocer que los procesos pueden conmutarentre maquinas

-

8/22/2019 procesamientoParalelo

46/65

Paralelizacion

Una sola aplicacion ejecutandose en paralelo en varias

maquinas en un clusterCompilador

Determina en tiempo de compilacion qu partes pueden serejecutadas en paralelo

Division para diferentes computadoras

AplicacionAplicacion escrita desde cero para ser paralelas

Paso de mensajes para enviar datos entre nodos

Dificil de programar

Mejor resultado final

Computacion parametrica Si un problema es la ejecucion repetida del algoritmo sobre

diferentes conjuntos de datos

Ejemplo: simulacion utilizando diferentes escenarios

Necesita herramientas efectivas para organizar y ejecutar

Arquitectura de Computadoras en

-

8/22/2019 procesamientoParalelo

47/65

Arquitectura de Computadoras en

Cluster

-

8/22/2019 procesamientoParalelo

48/65

Middelware de Cluster

Imagen unificada hacia el usuarioSingle system image

Unico punto de ingreso

Jerarquia de archivos unico

Unico punto de control Unica red virtual

Espacio de memoria unico

Sistema de gestion de trabajos unico

Interfaz de usuario unico Espacio de E/S unico

Espacio de proceso unico

Migracion de procesos

-

8/22/2019 procesamientoParalelo

49/65

Cluster v. SMP

Ambos propocionan soporte multiprocesador paraaplicaciones de alta demanda.

Ambos diponibles comercialmenteSMP por mas tiempo

SMP:Mas facil de manejar y controlar

Mas cercano a sistemas monoprocesador La planificacion es la diferencia principal

Menos espacio fisico

Menor consumo de energia

Clustering:Escalabilidad incremental y absoluta superior

Disponibilidad superior Redundancia

-

8/22/2019 procesamientoParalelo

50/65

Nonuniform Memory Access (NUMA)

Alternativa a SMP & clustering Uniform memory access Acceso Uniforme a Memoria

Todos los CPU tiene acceso a todas las partes de memoria

Tiempo de acceso a todas las regiones de memoria es el mismo

Tiempo de acceso a memoria para diferentes CPU es el mismo

Como se usa en SMP

-

8/22/2019 procesamientoParalelo

51/65

Nonuniform Memory Access (NUMA)

Nonuniform memory access

Acceso No uniforme a Memoria Todos los CPU tiene acceso a todas las partes de memoria

Tiempo de acceso de CPU difiere dependiendo de las regiones dememoria

Diferentes CPU acceden a diferentes regiones de memoria a diferentesvelocidades

Cache coherent NUMA La coherencia cache se mantiene entre las caches de los distintos CPU

Significativamente diferente de SMP y clusters

-

8/22/2019 procesamientoParalelo

52/65

Motivacin

SMP tiene limite practico de numero de CPUEl trafico del bus limita de 16 a 64 CPUs

En clusters, cada nodo tiene memoria propiaLas aplicaciones no ven la memoria global

Coherencia mantenida por software, no por hardware

NUMA mantiene caracteristicas SMP a la vez queproporciona multiprocesamiento a gran escalae.g. Silicon Graphics Origin NUMA: 1024 CPUs MIPS R10000

El objetivo es mantener un sistema de memoria

transparente en el sistema, permitiendo nodosmultiprocesador, cada uno con bus propio o unsistema de interconexion interna

-

8/22/2019 procesamientoParalelo

53/65

Organizacion CC-NUMA

-

8/22/2019 procesamientoParalelo

54/65

Operacion CC-NUMA

Cada CPU tiene su propia cacheL1 y L2

Cada nodo tiene su propiamemoria

Los nodos se conectan via alguntipo de red

Cada CPU ve un nico espaciodireccionable de memoria

Orden de requerimiento amemoria

Cache L1 (local para el CPU)

Cache L2 (local para el CPU) Memoria principal (local para el

nodo)

Memoria remota

Entregada al cache (local parael CPU) solicitante

Automatico y transparente

-

8/22/2019 procesamientoParalelo

55/65

Secuencia de acceso a Memoria

Cada nodo mantiene un directorio de la ubicacion de porciones dememoria y cache y su estado

Por ejemplo, el CPU 3 del nodo 2 (P2-3) solicita la posicion 798, lacual esta en la memoria del nodo 1

P2-3 envia una solicitud de lectura al bus snoopy del nodo 2 El directorio en el nodo 2 reconoce que la posicion esta en el nodo 1

El directorio del nodo 2 solicita el directorio del nodo 1

El directorio del nodo 1 solicita el contenido de 798

La memoria del nodo 1 pone el dato en el bus

El directorio del nodo 1 toma los datos del bus El dato se transfiere al directorio del nodo 2

El directorio del nodo 2 pone el datos en el bus (local del nodo 2)

Se toma el dato, se pone en cache de P2-3 y se entrega al CPU

-

8/22/2019 procesamientoParalelo

56/65

Coherencia Cache

El directorio del nodo 1 toma nota que el nodo 2 tieneuna copia del dato

Si el dato se modifica en cache esto se difunde a losdemas nodos

Los directorios locales monitorean y purgan la cachelocal de ser necesario

El directorio local monitorea los cambios a datos localesen caches remotas y marca la memoria como invalida

hasta una postescritura El directorio local fuerza una postescritura si la posicion

de memoria es solicitada por otro procesador

-

8/22/2019 procesamientoParalelo

57/65

NUMA: Pros & Cons

Rendimiento efectivo en niveles ms altos de

paralelismo que SMP No requiere cambios de software significativo

El rendimiento puede caer si se accede demasiado amemoria remota

Puede evitarse mediante: Diseo de cache L1 & L2 que reduzca el acceso a memoria

+ Se necesita buena localidad temporal del software

Buena localidad espacial del software

Administracion de memoria virtual que desplace pagina a los nodos

que ms los usan No es transparente

Se necesita cambios en asignacin de pginas, asignacin deprocesos y balanceo de carga

Disponibilidad?

-

8/22/2019 procesamientoParalelo

58/65

Computacion Vectorial

Problemas matematicos que implican procesos fisicos presentan

diferente dificultad para el computoAerodinamica, sismologia, meteorologia

Simulacion de campos contnuos

Alta precision

Calculos de punto flotante en arreglos numricos grandes

Las supercomputadoras manejan este tipo de problemas Cientos de millones de flops

$10-15 million

Optimizado para el calculo antes que para multitarea o E/S

Mercado limitado

Investigacion, agencias gubernamentales, meteorologia

Procesador matricial

Alternativa a las supercomputadoras

Configuradas como perifericos de mainframes y mini

Solo ejecutan las partes vectoriales de los problemas

-

8/22/2019 procesamientoParalelo

59/65

Ejemplode Suma Vectorial

-

8/22/2019 procesamientoParalelo

60/65

Enfoques

Las computadoras de proposito general se apoyan en

iteraciones para realizar calculo vectorial En el ejemplo, esto requiere seis iteraciones

Procesamiento vectorialAsume que es posible operar en un vector de datos

unidimensionalTodos los elementos en una fila pueden calcularse en paralelo

Procesamiento paraleloProcesadores independientes funcionan en paralelo

Se utiliza FORK N para iniciar un proceso en la posicion N

JOIN N permite que N procesos independientes se junten yfusionen

El Sistema operativo coordina los JOIN

La ejecucion se bloquea hasta que todos los N procesos alcancenJOIN

-

8/22/2019 procesamientoParalelo

61/65

Diseo de procesadores

ALUs encauzadosDentro de operacionesA traves de operaciones

ALUs paralelos

Procesadores paralelos

-

8/22/2019 procesamientoParalelo

62/65

Enfoques para la computacion vectorial

-

8/22/2019 procesamientoParalelo

63/65

Encadenamiento

Supercomputadoras Cray

Una operacion vectorial puede comenzar tanpronto como el primer elemento del operandovector este disponible y una unidad funcionaleste libre

El resultado de una unidad funcional alimentainmediatamente a otra

Si se utiliza vector de registros, los resultados

intermedios no tienen que ser almacenados enmemoria

-

8/22/2019 procesamientoParalelo

64/65

Organizacion de Computadores

-

8/22/2019 procesamientoParalelo

65/65

IBM 3090 con capacidad Vectorial