SesionII

-

Upload

stevend-meza-rodriguez -

Category

Documents

-

view

222 -

download

1

description

Transcript of SesionII

ELECTRÓNICA DIGITAL

SESIÓN II

SESIÓN II : Circuitos lógicos combinatorios.

OBJETIVOS

ÍNDICE

1. Suma de productos.2. Simplificación de circuitos lógicos.3. Simplificación algebraica.4. Diseño de circuitos lógicos combinatorios.5. Método del mapa de karnaugh.

INTRODUCCION

• En esta parte estudiaremos mas a fondo laaplicación de circuitos lógicos. Se utilizarandos métodos uno usa los teoremas del algebraBOOLEANA y el otro consiste en la técnica delmapeo. Además se tratara técnicas simplespara diseñar circuitos lógicos que satisfaganun conjunto determinado de requerimientos.

FORMA DE SUMA DE PRODUCTOS

• Los métodos de diseño y simplificación de circuitoslógicos que estudiaremos requieren que la expresiónlógica este en forma de SUMA DE PRODUCTOS,algunos ejemplos de esta forma son:

𝐴𝐵𝐶 + 𝐴𝐵 𝐶𝐴𝐵 + 𝐴𝐵 𝐶 + 𝐶 𝐷 + 𝐷

SIMPLIFICACION DE LOS CIRCUITOS LOGICOS

• Una vez que se ha obtenido la expresión paraun circuito lógico, podemos reducirla a unaforma mas simple que contenga menostérminos o variables en uno o mas términos. Lanueva expresión puede utilizarse para implantarun circuito que sea equivalente al original peroque contenga menos compuertas y conexiones.

EJEMPLO

SIMPLIFICACION ALGEBRAICA

• Los teoremas estudiados anteriormente sepueden utilizar para ayudarnos a simplificar laexpresión para un circuito lógico.Desafortunadamente, no siempre es obvio queteoremas deben aplicarse para producir elresultado mas simple. Además no existe unamanera sencilla de indicar si la expresiónsimplificada se encuentra en su forma mas simpleo si se puede simplificar aun mas.

• Así la simplificación algebraica se convierte en unproceso de ensayo y error. Sin embargo, conEXPERIENCIA uno puede llegar a obtenerresultados razonables y buenos.

EJEMPLO• Simplificar el siguiente circuito lógico que se

muestra en la figura

DISEÑO DE CIRCUITOS LOGICOS COMBINATORIOS

• Cuando se da el nivel de salida deseado de un circuito lógico en todas las posibles condiciones de entrada, los resultados se pueden mostrar adecuadamente en una tabla de verdad. La expresión booleana para el circuito requerido se puede determinar a partir de la tabla de verdad.

EJEMPLO

• Diseñe un circuito lógico que tenga 3 entradas A, B y C. el sistema tendrá una salida la cual solo será alta cuando la mayoría de las entradas sean altas.

EJEMPLO• Diseñe un circuito lógico que tenga 3 entradas

A, B y C. el sistema tendrá una salida la cual solo será alta cuando la mayoría de las entradas sean altas.

A B C X

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

PARA RECORDAR

TEOREMAS DE MORGAN

𝑋 + 𝑌 = 𝑋. 𝑌

𝑋. 𝑌 = 𝑋 + 𝑌

PROBLEMA

• Diseñe un circuito lógico que tenga 3 entradas A,B y C y cuya salida sea alta cuando la mayor parte de las entradas sea alta.

C B A X

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1 𝐴𝐵 𝐶

1 0 0 0

1 0 1 1 𝐶 𝐵𝐴

1 1 0 1 𝐶𝐵 𝐴

1 1 1 1 𝐴𝐵𝐶

PROBLEMA𝑋 = 𝐴𝐵 𝐶 + 𝐶 𝐵𝐴 + 𝐶𝐵 𝐴 + 𝐴𝐵𝐶

𝑋 = 𝐴𝐵 𝐶 + 𝐶 + 𝐶 𝐵𝐴 + 𝐶𝐵 𝐴

• 𝑋 = 𝐴𝐵 + 𝐶 𝐵𝐴 + 𝐶𝐵 𝐴

• 𝑋 = 𝐴 𝐵 + 𝐶 𝐵 + 𝐶 𝐵𝐴 + 𝐶𝐵 𝐴

• 𝑋 = 𝐴 𝐵 + 𝐶 + 𝐶 𝐵𝐴 + 𝐶𝐵 𝐴

• 𝑋 = 𝐴𝐵 + 𝐴𝐶 + 𝐶 𝐵𝐴 + 𝐶𝐵 𝐴

• 𝑋 = 𝐴𝐵 + 𝐴𝐶( 1 + 𝐵) + 𝐶𝐵 𝐴

• 𝑋 = 𝐴𝐵 + 𝐴𝐶+ 𝐶𝐵 𝐴

• 𝑋 = 𝐴𝐵 + 𝐶( A + 𝐵 𝐴 )

• 𝑋 = 𝐴𝐵 + 𝐶( A + 𝐵)

• 𝑋 = 𝐴𝐵 + 𝐴𝐶 + 𝐵𝐶

• 𝑋 = 𝐴(𝐵 + 𝐶 ) + 𝐵𝐶

PROBLEMA

• Se tiene un circuito combinacional (C.C.), donde se utilizan cuatro líneas de señales A, B, C y D para representar un numero binario de 4 bits con D como el (MSB) y A como (LSB). El circuito lógico produce una salida alta solo cuando el numero binario es mayor que 0110. diseñe este circuito.

D C B A Z

0 0 0 0 0

0 0 0 1 0

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 0

0 1 1 0 0

0 1 1 1 1

1 0 0 0 1

1 0 0 1 1

1 0 1 0 1

1 0 1 1 1

1 1 0 0 1

1 1 0 1 1

1 1 1 0 1

1 1 1 1 1

METODO DEL MAPA DE KARNAUGH

• Es un método grafico que se utiliza para simplificar una ecuación lógica para convertir una tabla de verdad a su circuito lógico correspondiente en un proceso simple y ordenado.

• Aunque este proceso se puede utilizar para resolver problemas con cualquier numero de variables de entrada, su utilidad practica se limita a 6 variables.

Reglas para el uso del mapa de Karnaugh:

• 1. Se elige para trabajar en mientras (minitéminos) o maxterms (maxitérminos).

• 2. en minterms o maxterms, se hace la menor cantidad de lazos o grupos con la mayor cantidad de unos (1) o ceros (0) respectivamente. Estos lazos solo pueden estar formados por potencias de 2, por lo tanto los grupos serán de 21, 22, 23, … 2n; donde podemos afirmar que el valor del exponente “n” será el numero de variables que se eliminaran al realizar la operación.

FORMATO DEL MAPA DE KARNAUGH

YY

𝑋 𝑋

𝑌00

101

0

𝑌10

011

1

Y X S

0 0 1

0 1 0

1 0 1

1 1 0

B C A S

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 0

1 1 1 0

𝐵 𝐵

𝐶000 001 011 010

𝐶100 101 111 110

𝐴 𝐴 𝐴

D C B A S

0 0 0 0 0

0 0 0 1 0

0 0 1 0 0

0 0 1 1 1

0 1 0 0 1

0 1 0 1 1

0 1 1 0 0

0 1 1 1 0

1 0 0 0 0

1 0 0 1 0

1 0 1 0 0

1 0 1 1 0

1 1 0 0 0

1 1 0 1 0

1 1 1 0 0

1 1 1 1 0

𝐵 𝐵

𝐷

0000 0001 0011 0010 𝐶

0100 0101 0111 0110

𝐶D

1100 1101 1111 1110

1000 1001 1011 1010 𝐶

𝐴 𝐴 𝐴

problemas

• Diseñe un sistema capaz de cubrir las necesidades de control de una pista de aterrizaje de un pequeño aeropuerto, el cual consta de 3 pistas llamadas A, B, y C.

• Un DC9 requiere solo una pista para aterrizar.

• Un B747 requiere 2 pistas.

B C A DC9 B747

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

𝐵 𝐵

𝐶000 001 011 010

𝐶100 101 111 110

𝐴 𝐴 𝐴

problemas• La imagen muestra el diagrama de una alarma para

automóvil empleada para detectar ciertas condiciones no deseables. Los tres interruptores se emplean para indicar el estado en el que se encuentra la puerta del conductor, el encendido y los faros respectivamente. Diseñe un circuito lógico con estos tres interruptores como entradas, de manera que la alarma se active cuando se presenten cualquiera de las siguientes condiciones.

• Los faros están prendidos mientras el carro este apagado.

• La puerta esta abierta mientras el carro esta prendido.

C.C. AUTOMOVIL

+5v

+5v

+5v

PUERTA

ENCENDIDO

LUCES

+5v

ALARMA

ALARMA PARA AUTOMOVIL

C B A S

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

𝐵 𝐵

𝐶000 001 011 010

𝐶100 101 111 110

𝐴 𝐴 𝐴

problemas

• La figura representa un detector de magnitud relativa que toma 2 números binarios de 2 bit, 𝑥1, 𝑥0 𝑦1, 𝑦0 este detector esta implementado para determinar si estos números son iguales, y si no lo son determina cual de ellos es el mayor.

DETECTORDE

MAGNITUD RELATIVA

𝑥0

𝑥1

𝑦0

𝑦1

𝑀 (𝑥 = 𝑦)

𝑁 (𝑥 > 𝑦)

𝑂(𝑥 < 𝑦)

problemasy1 y0 x1 x0 O N M

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

𝑥1 𝑥1

𝑦1

0000 0001 0011 0010𝑦0

0100 0101 0111 0110

𝑦0y1

1100 1101 1111 1110

1000 1001 1011 1010

𝑦0

𝑥0 𝑥0 𝑥0

SEMISUMADORS.S

A B

S

C

B A C S

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

Codificadores y decodificadores

Codificadores -decodificadores

• Los codificadores son sistemascombinacionales construidos en forma enforma de circuito integrado, que seencargan de transformar una serie deseñales sin codificar en un conjunto deseñales codificadas, que forman un código.

0 1 2 3 4 5 6 7 8 9 D C B A

1 0 0 0 0 0 0 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0 0 0 0 1

0 0 1 0 0 0 0 0 0 0 0 0 1 0

0 0 0 1 0 0 0 0 0 0 0 0 1 1

0 0 0 0 1 0 0 0 0 0 0 1 0 0

0 0 0 0 0 1 0 0 0 0 0 1 0 1

0 0 0 0 0 0 1 0 0 0 0 1 1 0

0 0 0 0 0 0 0 1 0 0 1 0 1 1

0 0 0 0 0 0 0 0 1 0 1 0 0 0

0 0 0 0 0 0 0 0 0 1 1 0 0 1

Codificadores - decodificadores• Los decodificadores son circuitos

integrados digitales que convierten el código binario o algún otro, en una forma sin codificar. Un decodificador, por tanto, puede considerarse lo opuesto de un codificador.

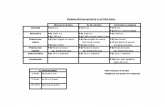

DECODIFICADOR BCD – 7 SEGEMNTOS

BCD-7 segmentos

• En el Excitador BCD-7 segmentos es un tipo de decodificador que me da la posibilidad de conectarlo a un display numérico digital de 7 segmentos a, b, c, d, e, f y g, obtener la visualización del código binario BCD:

D C B A QA QB QC QD QE QF QG

0 0 0 0 0 0 0 0 0 0 1

0 0 0 1 1 0 0 1 1 1 1

0 0 1 0 0 0 1 0 0 1 0

0 0 1 1 0 0 0 0 1 1 0

0 1 0 0 1 0 0 1 1 0 0

0 1 0 1 0 1 0 0 1 0 0

0 1 1 0 1 1 0 0 0 0 0

0 1 1 1 0 0 0 1 1 1 1

1 0 0 0 0 0 0 0 0 0 0

1 0 0 1 0 0 0 1 1 0 0

MULTIPLEXORES

DEFINICIÓNUn multiplexor digital es un circuito con 2n líneas deentrada de datos y una línea de salida; también debetener una manera de determinar la línea de entradade datos específica que se va a seleccionar encualquier momento. Esto se efectúa con otras nlíneas de entrada, denominadas entradas deselección, cuya función es elegir una de las 2n

entradas de datos para la conexión con la Salida.

APLICACIONES

Aquí algunas de sus aplicaciones:– Selector de entradas.– Serializador: Convierte datos desde el formato

paralelo al formato serie.– Transmisión multiplexada: Utilizando las mismas

líneas de conexión, se transmiten diferentes datosde distinta procedencia.

– Realización de funciones lógicas: Utilizando inversores y conectando a 0 ó 1 las entradas según interese, se consigue diseñar funciones complejas, de un modo más compacto que con las tradicionales puertas lógicas

8 entradas:

16 entradas:

2 entradas:

4 entradas:

Se representan en diagramas de bloques como trapezoides isósceles.

DIAGRAMA DE BLOQUES

TABLA DE VERDAD

DEMULTIPLEXORES

DEFINICIÓN

Realiza lo inverso a unmultiplexor (MUX), elcual tiene una sola salida,por la que ha de salir unade las varias entradasexistentes.

En electrónica digital, un demultiplexor (DEMUX) es uncircuito combinacional que tiene una entrada deinformación de datos y n entradas de control que sirvenpara seleccionar una de las 2n salidas, por la que ha desalir el dato que presente en la entrada.

APLICACIONES

La transferencia de información es una operaciónbásica en cualquier sistema digital. Aunque losdetalles internos del registro, la forma en que setransfiere la información desde el exterior alregistro y cómo sale de éste hacia el exterior, seránestudiados en su tema correspondiente,consideraremos en este caso la utilización demultiplexores y demultiplexores en el proceso detransferencia entre registros.

APLICACIONES

Según el valor de la señal de control, seselecciona qué entrada pasa a la salida delmultiplexor. Cuando se aplique el pulso detransferencia al registro, dicha señal desalida pasa al registro.

DEMULTIPLEXOR DE 2 BIT’S

D

S3

S2

S1

S0

A B

A B S3 S2 S1 S0

0 0 D - - -

0 1 - D - -

1 0 - - D -

1 1 - - - D