Universidad Nacional de Catamarca Facultad de Ciencias ...

Transcript of Universidad Nacional de Catamarca Facultad de Ciencias ...

Universidad Nacional de Catamarca

Facultad de Ciencias Exactas y Naturales Departamento: Informática y Comunicaciones

GUÍA DIDÁCTICA Arquitectura del Procesador I

Carrera: Tecnicatura en Informática Curso: Primer Año Plan: 2013 Composición de la Cátedra: Jefe de Cátedra: Ing. Georgina Inés Cerúsico J.T.P.: Esp. Ana Laura Palomeque

Año 2017

2

(1) FACULTAD DE: CIENCIAS EXACTAS Y NATURALES

(2) CARRERA: Tecnicatura en Informática

(3) N° DE ASIGNATURA (EN EL PLAN)

06

(4) CURSO 1ero.

(5) CUATRIMESTRE / ANUAL 2

(6) ASIGNATURA: Arquitectura del Procesador I

(7) PLAN DE ESTUDIOS: 2013

(8) CUERPO DOCENTE DE LA CÁTEDRA: a-Profesor Responsable de Cátedra

a.1- Nombre y Apellido: Ing. Georgina Inés Cerúsico de Tognola a.2- Cargo: Profesor Adjunto a.3-Dedicación funcional: Exclusiva b-Jefe de Trabajos Prácticos

b.1- Nombre y Apellido: Esp. Ana Laura Palomeque b.2- Cargo: Profesor Adjunto b.3-Dedicación funcional: Exclusiva c-Auxiliares Docentes

c.1- Nombre y Apellido: - c.2- Cargo: - c.3-Dedicación funcional: - d- Auxiliares Alumnos

d.1- Nombre y Apellido: - d.2- Cargo: - d.3-Dedicación funcional: -

(9) FUNDAMENTOS:

Esta asignatura introduce al alumno en el estudio de las arquitecturas de procesadores tomando como punto de partida los procesadores secuenciales de tipo Von Neumann.

El alumno realizará actividades que le permitirán comprender el funcionamiento de estos procesadores, tales como: resolver problemas de representación de los datos que serán manipulados por el procesador; efectuar prácticas en computadora que muestran los componentes del procesador que realizan la memorización y manipulación de los datos; conocer cuál es el conjunto de manipulaciones provistas habitualmente por los procesadores y cómo se

3

controla la realización de estas manipulaciones a medida que transcurre el tiempo.

Los contenidos mencionados permitirán el entendimiento de arquitecturas más avanzadas que intentan mejorar el rendimiento de los procesadores secuenciales. Temas que se abordarán en la asignatura Arquitectura del Procesador II en el segundo año de la carrera de Tecnicatura en Informática.

(10) OBJETIVOS:

* Comprender cómo se representan y se manipulan los datos a través de circuitos digitales.

* Comprender cómo están diseñados los procesadores secuenciales y cómo es su ciclo de

instrucción.

* Desarrollar una actitud crítica frente al diseño de distintos procesadores.

* Comprender cómo interactúan los procesadores con su medio externo.

* Obtener experiencia en programación de bajo nivel.

* Adquirir destreza en el manejo de la bibliografía especializada.

* Reforzar habilidades y actitudes relacionadas con el trabajo en grupo.

(11) METODOLOGIA

Unidades I, II, III, IV, V y VI: *Clases conferencia, seguidas de preguntas para responder o ejercicios para resolver

en clase, a modo de integración y cierre del tema abordado.

*Actividades de autoevaluación a través de formularios de Google, agregando una

nueva dimensión en la manera de reforzar los contenidos y acercar a los alumnos de

manera gradual a la modalidad de evaluación presencial tradicional.

*Prácticas en computadora sobre temas de la teoría.

*Cuestionarios individuales y grupales.

*Discusión de temas en pequeños grupos, analizando artículos de revistas

especializadas o de sitios de Internet vinculados con los sistemas digitales.

*Estudio independiente.

*Clases Prácticas sobre simplificación de expresiones booleanas utilizando el

Software Karnaugh Map Minimizer o similar.

*Clases Prácticas sobre construcción de circuitos lógicos digitales utilizando el

Software Multimedia Logic o similar.

*Clases Prácticas sobre Programación en Ensamblador.

*Consulta de material bibliográfico.

Número y carácter de las clases:

*30 teóricas/teórico-prácticas, 14 prácticas/teórico-prácticas.

4

(12) SISTEMA DE EVALUACIÓN Se tomarán 3 ( tres) exámenes parciales,

Se tomará una evaluación en máquina que constará de dos partes: simplificación de

expresiones booleanas utilizando el Software Karnaugh Map Minimizer y la construcción

de circuitos lógicos digitales utilizando el Software Multimedia Logic (o similar), y la

Programación en Lenguaje Ensamblador.

Se requerirá la realización de un Trabajo Especial tipo monográfico sobre

Evolución de Procesadores.

Se implementarán trabajos de control en clase al final de las mismas, y también

trabajos extraclase, como: cuestionarios, ejercicios y problemas. Se realizarán actividades

de autoevaluación a través de formularios de Google.

La clasificación de los exámenes, evaluaciones y del Trabajo Especial Grupal será

con la escala de 0 a 10, mientras que los trabajos prácticos serán aprobados o

desaprobados. Podrán recuperarse dos parciales y la evaluación práctica, los trabajos

prácticos deberán rehacerse hasta que sean aprobados.

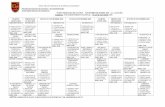

Aspecto Criterio Instrumento Peso

Asistencia y Participación

‐Participación activa en la clase. ‐Participación en los debates -Participación en el trabajo Grupal

‐Observación y notas del Profesor.

15%

Conceptos de la materia

‐Dominio de los conocimientos teóricos y operativos de la materia.

-Examen teórico (prueba objetiva) Presentación del trabajo especial grupal. -Resultados de las autoevaluaciones con formularios de Google.

50%

Conceptos prácticos de la materia

- Dominio de los conocimientos sobre Programación en Lenguaje Ensamblador

Examen práctico (evaluación individual en máquina)

30%

Aportaciones libres de los alumnos

-Pertinencia de la actuación al contenido de la materia. -Calidad de la actividad o el material aportado.

Valoración del producto o actividad.

5%

5

Reglamento de Cátedra:

* Si el alumno obtuviese en cada una de las evaluaciones o su recuperatorio una nota

mayor o igual a 4 (cuatro) y menor a 7 (siete), y deberá rendir examen final de los

contenidos de la asignatura.

* Si el alumno obtuviese en cada una de las evaluaciones o su recuperatorio una nota

mayor o igual a 7 (siete), se considera que ha promocionado la asignatura, por lo que se

dará por aprobada la asignatura.

* Si el alumno obtuviese como máximo, en alguna de las evaluaciones o su

recuperatorio una nota menor a 4 (cuatro), deberá rendir en el examen final los contenidos

teóricos y prácticos de la asignatura. Es decir, el examen libre constará de dos partes: una

práctica, en la computadora, sobre simplificación de expresiones booleanas utilizando el

Software Karnaugh Map Minimizer y la construcción de circuitos lógicos digitales

utilizando el Software Multimedia Logic (o similar) y la programación en Ensamblador; y

otra, que incluirá los contenidos teóricos de la materia actualizados al programa vigente al

momento de rendir, que se tomará sólo cuando el alumno haya aprobado el examen

práctico. El alumno que desee presentarse a rendir como “libre” debe comunicarlo a los

docentes de la Cátedra por lo menos 7 (siete) días antes de la fecha del examen.

* Tanto para la regularización como para la promoción de la asignatura, el alumno

deberá: tener un 80 % de asistencia a clases, tanto prácticas como teóricas, y aprobar el

100 % de los exámenes parciales y la evaluación práctica, o sus recuperatorios. Asimismo,

deberá aprobar la presentación del Trabajo Especial Grupal, y deberá completar y

presentar en tiempo y forma, todos los trabajos extraclase y autoevaciones que se

requieran.

(13) CONTENIDOS MINIMOS: Sistemas digitales: sistemas combinatorios y secuenciales, autómatas; circuitos básicos. Representación de la información: alfanumérico, punto fijo y flotante, representación de signo, complemento a 1 y a 2. Estructura de una computadora: máquina Von Neumann, máquina algorítmica (Gluskov), UCP, ALU, memorias, periféricos, procesadores de entrada-salida, buses. Assemblers, registros accesibles al programador, ciclos de búsqueda, ejecución de instrucción, buses internos, mecanismos de acceso a memorias, memorias entrelazadas, formato y conjunto de instrucciones, direccionamiento, subrutinas, interrupciones y excepciones. Programación en assembler, detección de

errores o debugging o, en su defecto, usando simuladores.

(14) PROGRAMA ANALITICO:

6

Programa de Contenidos teóricos Unidad N° 1: Introducción a los sistemas digitales.

Compuertas lógicas: AND, OR, NOT, XOR, NAND, NOR. Álgebra de Boole. Circuitos

combinacionales. Tablas de verdad y diagramas lógicos. Simplificación por mapas.

Circuito semisumador, circuito sumador completo. Decodificador. Circuitos secuenciales.

Flip-Flops: SR, D, JK, T. Tablas de excitación. Ecuaciones de entrada de los circuitos

secuenciales, tabla y diagrama de estado. Registros.

Unidad N° 2: Representación de datos. Sistemas Numéricos y Aritmética.

Sistemas numéricos posicionales. Sistema binario, hexadecimal y octal. Cambios de base.

Complementos. Complemento r-1. Complemento a r. Aritmética de números sin signo no

fraccionarios. Representación de punto fijo. Representación de enteros. Representación de

números negativos: representación signo y magnitud, representación de complemento a 2

con signo, representación de complemento a 1 con signo. Suma aritmética. Resta

aritmética. Sobreflujo. Representación de números fraccionarios: representación en punto

fijo y representación con punto flotante. Número de punto flotante normalizado.

Representación de caracteres. Otros códigos binarios. Código BCD, ASCII.

Unidad N° 3: Organización básica de una Computadora.

Organización de programa almacenado. Organización de un sistema de computadora:

unidad central de procesamiento (CPU), memoria, entrada/salida (I/O) y sistema de

interconexión (buses). Entrada-salida e Interrupción.

Organización básica de la CPU: unidad de control, unidad aritmética y lógica, registros y

buses internos. Códigos de instrucción. Direccionamiento directo e indirecto. Conjunto de

instrucciones. Ciclo de instrucción. Formatos de las instrucciones. Instrucciones de tres

direcciones, de dos direcciones, de una dirección o cero direcciones. Modos de

direccionamiento: Implícito, inmediato, registro, indirecto por registro, autoincremento o

autodecremento, relativo, indexado, registro base.

Procesadores CISC y RISC. Características.

Operaciones: de transferencia de datos, aritméticas, de manejo de bits, de manejo de

cadenas, de interrupción, de control del microprocesador y de transferencia de control.

Unidad N° 4: Programación básica de la computadora.

Lenguaje de máquina. Lenguaje ensamblador: conceptos generales, sintaxis y código

nemónico. Ensamblador de dos pasadas. Representación de un programa simbólico en la

memoria. Programación básica. Ejemplos de programas en lenguaje ensamblador Familia

Intel.

Unidad N° 5: Entrada/Salida.

Módulos de entrada/salida: interfaz con la CPU e interfaz con el dispositivo. Protocolos de

entrada/salida. Entrada/Salida programada. Organización de la entrada/salida: dedicada o

inmersa en memoria. Ejemplos de la entrada/salida.

Unidad N° 6: Interrupciones. Acceso directo a memoria.

Cambios de contexto. Estructura lógica del sistema de interrupción. Prioridades y

habilitación de interrupciones. Acceso directo a memoria. Robo de ciclo.

Programa de Contenidos prácticos:

7

Trabajo Práctico N° 1: Circuitos combinacionales y secuenciales. Trabajo Práctico N° 2: Registros Internos del Microprocesador. Trabajo Práctico N° 3: Ensamblador: Clasificación de instrucciones y Sintaxis. Trabajo Práctico N° 4: Ensamblador: Resolución de problemas.

(15) CRONOGRAMA DE ACTIVIDADES

SEMANA CONTENIDOS METODOLOGÍA

DESCRIPCION DE TAREAS DEL

ALUMNO (presencial y no presencial)

Horas

presenciales

(previsión)

CONTENIDOS TEÓRICOS

1

Unidad I Clase magistral participativa

Asistencia y participación Puesta en común de

conocimientos previos Debate

Estudio personal

6 Hs.

2 Unidad I

Clase magistral

participativa

Asistencia y participación Estudio personal

Resolución de problemas y/o

ejercicios

6 Hs.

3

Unidad I

Resolución de

Práctico

preparatorio 1er. Parcial

Asistencia y participación Resolución de problemas y/o

ejercicios

6 Hs.

4 Unidad I y II

Evaluación Resolución de

problemas

Asistencia y participación Resolución de problemas y/o

ejercicios

6 Hs.

5 Unidad II

Clase magistral

participativa

Asistencia y participación Resolución de problemas y/o

ejercicios

6 Hs.

6 Unidad II

Clase magistral

participativa

Asistencia y participación Estudio personal

Resolución de problemas y/o ejercicios

6 Hs.

7

Unidad II

Clase magistral

participativa. Resolución de

Práctico

preparatorio 2do. Parcial

Evaluación

Asistencia y participación

Estudio personal Resolución de problemas y/o

ejercicios

6 Hs.

8 Unidad III

Clase magistral participativa

Asistencia y participación

Resolución de problemas y/o

ejercicios

6 Hs.

9 Unidad III Clase magistral

participativa

Asistencia y participación

Estudio personal 6 Hs.

10 Unidad IV Clase magistral participativa

Asistencia y participación Estudio personal

6 Hs.

11 Unidad V

Clase magistral

participativa

Asistencia y participación Resolución de problemas y/o

ejercicios

Estudio personal

6 Hs.

8

12

Unidad V y VI Clase magistral participativa

Asistencia y participación

Resolución de problemas y/o ejercicios

Estudio personal

6 Hs.

13 Unidad VI Clase magistral

participativa

Asistencia y participación

Estudio personal 6 Hs.

14

Unidades III a VI

Clase de

Consulta.

Resolución de Práctico

preparatorio 3er. Parcial

Evaluación

Preparación para el examen y realización del mismo. Consulta.

6 Hs.

15

Todas las

Unidades

Clase de Consulta

Evaluación

Preparación para el examen y

realización del mismo. Consulta. 6 Hs.

Total = 90 hs.

CONTENIDOS PRÁCTICOS

SEMANA CONTENIDOS METODOLOGÍA DESCRIPCIÓN TAREAS DEL

ALUMNO

HORAS

PRESENCIALES

1

Trabajo Práctico

n° 1 Circuitos

Combinacionales y secuenciales

Práctica guiada Adquisición de datos – Trabajo en

grupo.

2 Hs.

2 Trabajo Práctico n° 1 Circuitos

Combinacionales y secuenciales

Resolución de trabajo práctico

Resolución de ejercicios – Trabajo en grupo.

2 Hs.

3 Trabajo Práctico

n° 1 Circuitos Combinacionales

y secuenciales

Resolución de

trabajo práctico

Resolución de ejercicios – Trabajo

en grupo.

2 Hs.

4 Trabajo Práctico

n° 2 Registros Internos

Práctica guiada Adquisición de datos – Trabajo en

grupo.

2 Hs.

5 Trabajo práctico n° 2: Registros

Internos

Resolución de trabajo práctico

Resolución de ejercicios – Trabajo en grupo.

2 Hs.

6 Trabajo práctico

n° 3:

Ensamblador: Clasificación de

instrucciones y Sintaxis

Práctica guiada Adquisición de datos – Trabajo en

grupo.

2 Hs.

7 Trabajo práctico n° 3:

Ensamblador:

Clasificación de instrucciones y

Resolución de trabajo práctico

Resolución de ejercicios – Trabajo en grupo.

2 Hs.

9

Sintaxis

8 Trabajo práctico

n° 3: Ensamblador:

Clasificación de

instrucciones y Sintaxis

Resolución de

trabajo práctico

Resolución de ejercicios – Trabajo

en grupo.

2 Hs.

9 Trabajo práctico n° 4:

Ensamblador: Resolución de

problemas

Práctica guiada Adquisición de datos – Trabajo en grupo.

2 Hs.

10 Trabajo práctico

n° 4:

Ensamblador: Resolución de

problemas

Resolución de

trabajo práctico

Adquisición de datos – Trabajo en

grupo.

2 Hs.

11 Trabajo práctico

n° 4: Ensamblador:

Resolución de

problemas

Resolución de

trabajo práctico

Adquisición de datos – Trabajo en

grupo.

2 Hs.

12 Evaluación de

prácticos

Evaluación

individual en la máquina

Preparación para el examen y

realización del mismo.

2 Hs.

13 Consulta para recuperatorio

Consulta libre Realización de ejercicios – Trabajo en grupo. Consulta.

2 Hs.

14 Recuperatorio Evaluación

individual en la

máquina

Preparación para el examen y realización del mismo.

2 Hs.

Total = 28 hs.

10

(16) RECURSOS DE ENSEÑANZA APRENDIZAJE: Bibliografía Básica: Unidad I:

-Molina Marticorena, José Luis.Circuitos Integrados.Disponible en

http://www.profesormolina.com.ar/electronica/componentes/int/index.htm - Costantini, Sandro.Cátedra Arquitectura del Procesador. Universidad Metropolitana de

Venezuela. 2013.

Unidad II:

- Martí Campoy, Antonio. Representación de Enteros. Signo y Magnitud. Complemento

a 1. Complemento a 2. Universidad Politécnica de Valencia. 2011. Disponible en:

https://www.youtube.com/watch?v=xyGXtdJpiDg

- Santamaría, Pablo. Representación de los números en la computadora. Facultad de

Ciencias Astronómicas y Geofísicas. Universidad Nacional de la Plata. 2009. Disponible en:

http://www.famaf.unc.edu.ar/~vmarconi/fiscomp/representacion-numeros.pdf

Todas las unidades: -Patterson, David A. y Hennessy, JohnL.Estructura y diseño de computadores. La

interfaz hardware / software.Ed. Reverte. 2011.

- Mano, M. Morris.Arquitectura de Computadoras. Tercera Edición. Prentice-Hall

Hispanoamericana. 1995.

- Rodríguez Roselló, Miguel Angel. Programación Ensamblador en entorno MS-

DOS.Anaya Multimedia. 1988.

- Hennessy, .John L. y Patterson, David A. Computer Architecture: A Quantitative

Approach. Ed. Morgan Kaufman. 2001.

- Wilkinson, Barry. Computer Architecture: Design And Performance.Prentice Hall

International. 2ª Edition. 1996.

- Stallings. W. Organización y Arquitectura de Computadores. 5ª Edicion. Prentice Hall

2000.

- Cerúsico, Georgina Inés. Notas de Cátedra. 2017.

- Cerúsico, Georgina Inés. Página WEB de la asignatura: www.actiweb.es/arqproc1unca

Bibliografía complementaria: Todas las unidades:

- Brookshear, J. Glenn. Introducción a las Ciencias de la Computación. Cuarta Edición.

Addison-Wesley Iberoamericana. 1995.

- Tischer, Michael. Jennrich, Bruno. PC Interno Programación de sistema. Marcombo.

1996.

Otros: Páginas Web y Materiales relacionadas con la Arquitectura de los procesadores. Guías de prácticos y material de apoyo confeccionado por los docentes de la cátedra.

Ing. Georgina Inés Cerúsico de Tognola

Marzo 2017